# Dissecting 1t1synt

Florian Renkin<sup>1\*</sup>, Philipp Schlehuber-Caissier<sup>1</sup>, Alexandre Duret-Lutz<sup>1</sup> and Adrien Pommellet<sup>1</sup>

<sup>1</sup>EPITA Research Laboratory, EPITA, 14–16 rue Voltaire, 94270 Kremlin-Bicêtre, France.

\*Corresponding author(s). E-mail(s): renkin@lrde.epita.fr; Contributing authors: philipp@lrde.epita.fr; adl@lrde.epita.fr; adrien@lrde.epita.fr;

#### Abstract

ltlsynt is a tool for synthesizing a reactive circuit satisfying a specification expressed as an LTL formula. ltlsynt generally follows a textbook approach: the LTL specification is translated into a parity game whose winning strategy can be seen as a Mealy machine modeling a valid controller. This article details each step of this approach, and presents various refinements integrated over the years. Some of these refinements are unique to ltlsynt: for instance, ltlsynt supports multiple ways to encode a Mealy machine as an AIG circuit, features multiple simplification algorithms for the intermediate Mealy machine, and bypasses the usual game-theoretic approach for some subclasses of LTL formulas in favor of more direct constructions.

**Data Availability Statement:** Instructions to reproduce the benchmarks presented in this article are available from https://www.lrde.epita.fr/~frenkin/fmsd22/artifact

**Keywords:** reactive synthesis, Mealy machines, parity automata, parity games, LTL formulas

#### 1 Introduction

Program synthesis is a well-established formal method: given a logical specification of a system, it allows one to automatically generate a provably correct implementation. It can be applied to *reactive controllers* (Fig. 1), that is, circuits that read an input stream of Boolean valuations (here, over Boolean variables *a* and *b*) and

Fig. 1: A reactive controller, seen as a black box that reads some input signals (here a, b) to produce some output signals (here x, y).

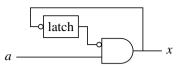

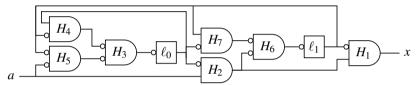

Fig. 2: An And-Inverter Graph where the latch is used to remember if a has been false. Output x is true as long as a remains true, and becomes continuously false on the first occurrence of  $\bar{a}$ .

is odd.

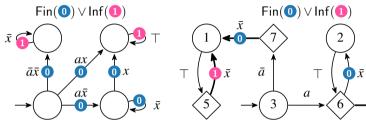

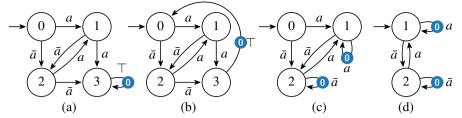

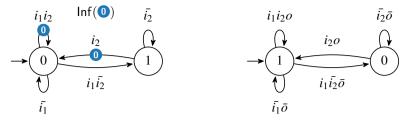

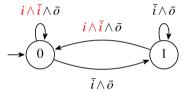

Fig. 3: A deterministic max Fig. 4: The two-player parity game interpretation of odd parity automaton for the automaton of Fig. 3. Player 0 plays from round  $a \leftrightarrow F(x)$ . An infinite run nodes and selects input signals; player 1 plays from is accepting if the maximal square nodes and selects output signals. The game is color it visits infinitely often winning for player 1 if, regardless of the choices made by player 0, player 1 can force the infinite play to satisfy the parity max odd acceptance condition. This is the case here if player 1 always selects the thick transitions.

simultaneously produce a matching output stream of valuations (here, over x and y). The ltlsynt tool that we shall discuss solves this problem when the specification is given as a Linear-time Temporal Logic formula constraining the input and output signals over time. If this specification is realizable, that is, if it is possible to build a controller for it, then the output is expected as an And-Inverter Graph (AIG), that is, a circuit built from and gates , negations o, and latches that delay their input by one tick, and output 0 initially.

For instance, assuming a single input signal a and a single output signal x, the specification formula  $a \leftrightarrow F(x)$ , which states that a should hold initially if and only if x holds eventually, could be satisfied by constructing a controller such that the Boolean output value x is continuously equal to the first value of the Boolean input a. However, many other controllers could satisfy this formula. For instance, in Fig. 2, signal x holds until the first  $\bar{a}$  is received, and remains false after that occurrence. Among possible choices, we are interested in producing a small controller in terms of AIG size (number of gates and latches).

**Fig. 5**: The winning strategy of Fig. 4, seen as an incompletely specified Mealy machine.

**Fig. 6**: A reduced Mealy machine, for the winning strategy of Fig. 4. Note how the states of this machine are used to remember if  $\bar{a}$  has been seen at some point. This machine can be encoded into the AIG of Fig. 2.

To obtain the AIG controller, we use an automata-theoretic approach whose main steps are the following:

- Convert the specification LTL formula into a deterministic parity automaton (Fig. 3).

- Knowing that output signals are controllable while input signals are not, convert this parity automaton into a parity game, where player 0 (the environment) chooses the input signals, and player 1 (the controller) chooses the output signals. In addition to being deterministic, this game has to be input complete, i.e., the environment must always be able to select any valuation of the input signals (Fig. 4). The specification is realizable if player 1 has a strategy to respond to any input stream while satisfying the parity acceptance condition.

- A winning strategy for player 1 can be seen as a Mealy machine (Fig. 5). We use incompletely specified generalized Mealy machines to capture some of the freedom provided by the strategy as far as output selection is concerned.

- The above Mealy machine is then reduced (Fig. 6), taking advantage of that freedom if possible.

- Finally the Mealy machine is encoded in the AIGER format, to represent the controller as an AIG (Fig. 2).

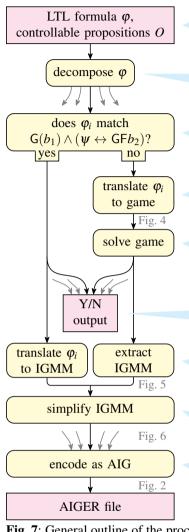

The above steps are a mere outline of the procedure implemented in our tool, called ltlsynt, and distributed along with the Spot library (Duret-Lutz et al, 2022), where most of the operations are implemented. Figure 7 gives a more detailed picture by including two optimizations: a decomposition of the specification into multiple sub-specifications (we refer the reader to Finkbeiner et al (2021) for more details about this technique), and a shortcut to the "standard" construction for some LTL formulas.

The rest of this article is organized as follows. We define LTL, automata, parity games, and Mealy machines in Section 2. The rest of the sections delve into specific steps of this pipeline: Section 3 explains how we convert LTL formulas into deterministic parity automata, Section 4 discusses different options for reducing incompletely specified Mealy machines, Section 5 discusses several ways to encode our Mealy

The user supplies the specification of a reactive system using an LTL formula tying some uncontrollable input signals to some controllable output signals.

Optionally decompose  $\varphi = \bigwedge_i \varphi_i$  as a conjunction of subspecifications  $\varphi_i$  with independent outputs. (Finkbeiner et al, 2021)

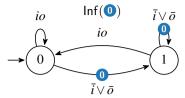

For this subclass of formulas, we can bypass the game-theoretical framework. (Section 6)

$\varphi_i$  is converted to a parity game where player 0 plays the input signals, and player 1 plays the output signals. (Section 3)

The game is solved using a variant of Zielonka's algorithm (van Dijk, 2018). A controller is realizable if player 1 has a winning strategy for the initial state.

When ltlsynt is called with option --realizability, the process can stop here by combining the results of all  $\varphi_i$ s.

Otherwise, an Incompletely specified Generalized Mealy Machine (IGMM) is created from the winning strategy, or from  $\varphi_i$ .

Simplifying the IGMM helps to reduce the size of the controller. (Section 4)

Encoding as an And-Inverter Graph can be done in a number of ways. Combining the different "sub-controllers" for the  $\varphi_i$ s is done in this step. (Section 5)

**Fig. 7**: General outline of the process used by ltlsynt to solve a reactive synthesis problem.

machines into an AIG. Section 6 shows how to bypass the "standard" construction for some subclass of LTL formulas. Finally we evaluate some of these choices in Section 7.

# 2 Concepts

#### 2.1 Valuations and Cubes

Let  $\mathbb{N} = \{0,1,2,\ldots\}$  be the set of natural numbers, and let  $\mathbb{B} = \{\top,\bot\}$  denote the set of Boolean values. Given a set X of propositions (i.e., Boolean variables), a *valuation* is a function from X to  $\mathbb{B}$ . Let  $\mathbb{B}^X$  be the set of all possible valuations on X, and let  $2^{\mathbb{B}^X}$  be its set of subsets. Any element of  $2^{\mathbb{B}^X}$  can be expressed as a Boolean formula over X, so we shall often represent valuations or set of valuations as Boolean formulas over X. The negation of proposition p is denoted  $\bar{p}$ . We overload  $\top$  (resp.  $\bot$ ) to denote the Boolean formula that is always true (resp. false), or equivalently the set  $\mathbb{B}^X$  (resp.  $\emptyset$ ), and assume that X is clear from the context.

A *cube* is a (possibly empty) conjunction of propositions or their negations (i.e., literals). As an example, given three propositions  $X = \{a, b, c\}$ , the cube  $a \wedge \bar{b}$ , usually written  $a\bar{b}$ , stands for the set of valuations in which a is true and b is false, i.e.,  $\{a\bar{b}c, a\bar{b}\bar{c}\}$ . Let  $\mathbb{K}^X$  stand for the set of all cubes over X.  $\mathbb{K}^X$  contains the cube  $\top$  (the empty conjunction), that stands for the set of all possible valuations over X. Note that any set of valuations can be represented as a disjunction of disjoint cubes.

#### 2.2 Linear-Time Temporal Logic

Given an alphabet  $\Sigma$ , we use  $\Sigma^{\omega}$  to denote the set of infinite words over  $\Sigma$ . For a word  $\pi = \pi_0 \pi_1 \pi_2 \ldots \in \Sigma^{\omega}$  we note  $\pi_i$  its letter at position  $i \in \mathbb{N}$ . We use  $\pi_{i..}$  to denote the suffix of  $\pi$  starting at position i, in other words  $\pi_i \pi_{i+1} \pi_{i+2} \ldots = \pi_{i..}$ .

A set of words  $L \subseteq \Sigma^{\omega}$  is called a language. We note  $L^{\mathbb{C}} = \Sigma^{\omega} \setminus L$  its complement. In the sequel, we work with an alphabet that contains valuations over a set of input and output propositions (representing the input and output signals of our controller). Let I and O be two disjoint sets of input and output propositions. A *trace* is an infinite word  $\pi \in (\mathbb{B}^{I \cup O})^{\omega}$  over valuations of  $I \cup O$ . We use symbol  $\cup$  to indicate that this is a disjoint union.

A classical formalism to express specifications on traces is LTL:

**Definition 1** (LTL) A *Linear-time Temporal Logic* formula is built from the following grammar:

$$\varphi ::= \top \mid \bot \mid p \mid \neg \varphi \mid \varphi \odot \varphi \mid \mathsf{F} \varphi \mid \mathsf{G} \varphi \mid \mathsf{X} \varphi \mid \varphi \, \mathsf{U} \varphi \mid \varphi \, \mathsf{R} \varphi$$

where  $p \in I \cup O$  is any proposition, and  $\odot \in \{\land, \lor, \rightarrow, \leftrightarrow, \oplus\}$  represents any binary Boolean operator  $(\oplus$  is exclusive or).

Parentheses are used for grouping, but we omit them from the above grammar and the upcoming ones for simplicity.

**Definition 2** (Semantics of LTL) For a trace  $\pi \in (\mathbb{B}^{I \cup O})^{\omega}$  and an LTL formula  $\varphi$ , we say that  $\pi$  satisfies  $\varphi$ , denoted  $\pi \models \varphi$ , and define this relation inductively as follows:

$$\pi \vDash \bot \Leftrightarrow \bot

\pi \vDash \rho \Leftrightarrow \pi_0(\rho) = \top

\pi \vDash \neg \varphi \Leftrightarrow \neg(\pi \vDash \varphi)

\pi \vDash \varphi \odot \psi \Leftrightarrow (\pi \vDash \varphi) \odot (\pi \vDash \psi)

\pi \vDash X\varphi \Leftrightarrow \pi_{1..} \vDash \varphi

\pi \vDash F\varphi \Leftrightarrow \exists i \in \mathbb{N}, \pi_{i..} \vDash \varphi

\pi \vDash G\varphi \Leftrightarrow \forall i \in \mathbb{N}, \pi_{i..} \vDash \varphi

\pi \vDash \varphi \cup \psi \Leftrightarrow \exists i \in \mathbb{N}, \pi_{i..} \vDash \psi \text{ and } \forall j \in \{0, \dots, i-1\}, \pi_{j..} \vDash \varphi

\pi \vDash \varphi R \psi \Leftrightarrow \begin{cases} \forall i \in \mathbb{N}, \pi_{i..} \vDash \psi \text{ or } \\ \exists i \in \mathbb{N}, \pi_{i..} \vDash \varphi \text{ and } \forall j \leq i, \pi_{j..} \vDash \psi \end{cases}$$

In the above,  $\rho \in I \cup O$  is a proposition,  $\varphi$  and  $\psi$  are LTL formulas, and  $\odot \in \{\land, \lor, \rightarrow, \leftrightarrow, \oplus\}$  is any binary Boolean operator.

The language of a formula  $\varphi$  is the set of traces that satisfy it:  $\mathscr{L}(\varphi) = \{\pi \in (\mathbb{B}^{I \cup O})^{\omega} \mid \pi \vDash \varphi\}$ . Two formulas  $\varphi$  and  $\psi$  are said to be *equivalent* if they have the same language, and we write  $\varphi \equiv \psi$ .

We now define some useful subclasses of LTL formulas.

**Definition 3** (Some subclasses of LTL) Consider the following grammar rules, where  $p \in I \cup O$  is any proposition,  $\Theta \in \{\land, \lor, \leftrightarrow, \oplus\}$  is any commutative Boolean operator,  $\odot \in \{\land, \lor, \rightarrow, \leftrightarrow, \oplus\}$  is any binary Boolean operator, and  $\varphi$  is any LTL formula.

$$\begin{split} \phi_N &::= \top \mid \bot \mid p \mid \neg p \mid \phi_N \ominus \phi_N \mid \mathsf{F}\phi_N \mid \mathsf{G}\phi_N \mid \mathsf{X}\phi_N \mid \phi_N \cup \phi_N \mid \phi_N \, \mathsf{R}\, \phi_N \\ \phi_X &::= \top \mid \bot \mid p \mid \neg \phi_X \mid \phi_X \odot \phi_X \mid \mathsf{X}\phi_X \\ \phi_G &::= \phi_X \mid \neg \phi_S \mid \phi_G \wedge \phi_G \mid \phi_G \vee \phi_G \mid \phi_S \rightarrow \phi_G \mid \mathsf{X}\phi_G \mid \mathsf{F}\phi_G \mid \phi_G \cup \phi_G \\ \phi_S &::= \phi_X \mid \neg \phi_G \mid \phi_S \wedge \phi_S \mid \phi_S \vee \phi_S \mid \phi_G \rightarrow \phi_S \mid \mathsf{X}\phi_S \mid \mathsf{G}\phi_S \mid \phi_S \, \mathsf{R}\, \phi_S \\ \phi_O &::= \phi_G \mid \phi_S \mid \neg \phi_O \mid \phi_O \odot \phi_O \mid \mathsf{X}\phi_O \mid \phi_O \cup \phi_G \mid \phi_O \, \mathsf{R}\, \phi_S \\ \phi_P &::= \phi_O \mid \neg \phi_R \mid \phi_P \odot \phi_P \mid \mathsf{X}\phi_P \mid \mathsf{F}\phi_P \mid \phi_P \cup \phi_P \mid \phi_P \, \mathsf{R}\, \phi_S \\ \phi_R &::= \phi_O \mid \neg \phi_P \mid \phi_R \odot \phi_R \mid \mathsf{X}\phi_R \mid \mathsf{G}\phi_R \mid \phi_R \cup \phi_G \mid \phi_R \, \mathsf{R}\, \phi_R \\ \phi_\mu &::= \bot \mid \top \mid \neg \phi_V \mid \phi_\mu \wedge \phi_\mu \mid \phi_\mu \vee \phi_\mu \mid \mathsf{X}\phi_\mu \mid \mathsf{F}\phi \mid \mathsf{G}\phi_\mu \mid \phi \cup \phi_\mu \mid \top \cup \phi \mid \phi_\mu \, \mathsf{R}\, \phi_\mu \\ \phi_V &::= \bot \mid \top \mid \neg \phi_\mu \mid \phi_V \wedge \phi_V \mid \phi_V \vee \phi_V \mid \mathsf{X}\phi_V \mid \mathsf{F}\phi_V \mid \mathsf{G}\phi \mid \phi_V \cup \phi_V \mid \phi \, \mathsf{R}\, \phi_V \mid \bot \, \mathsf{R}\, \phi \\ \phi_\xi &::= \bot \mid \top \mid \neg \phi_\xi \mid \phi_\xi \odot \phi_\xi \mid \mathsf{F}\phi_V \mid \mathsf{G}\phi_\mu \mid \mathsf{F}\phi_\xi \mid \mathsf{G}\phi_\xi \mid \mathsf{X}\phi_\xi \mid \phi \cup \phi_\xi \mid \phi \, \mathsf{R}\, \phi_\xi \\ \end{split}$$

Formulas produced by rule  $\varphi_N$  are said to be in *negative normal form* (NNF): i.e., negation is only applied to atomic propositions, and implication is not used.

Formulas produced by rule  $\varphi_X$  are LTL(X) formulas, i.e., LTL formulas where the only temporal operator used is X.

Formulas produced by rules  $\varphi_G$ ,  $\varphi_S$ ,  $\varphi_O$ ,  $\varphi_P$ ,  $\varphi_R$  are called respectively *syntactic guarantee formulas*, *syntactic safety formulas*, *syntactic obligation formulas*, *syntactic persistence formulas* and *syntactic recurrence formulas* (Černá and Pelánek, 2003).

Formulas produced by rules  $\varphi_{\mu}$ ,  $\varphi_{V}$ , and  $\varphi_{\xi}$  are called respectively *pure eventuality formulas*, *pure universality formulas*, and *suspendable formulas* (Babiak et al, 2013).

**Theorem 2.1** (Folklore) Any LTL formula can be transformed into an equivalent NNF formula by pushing negations inward, applying rules such as  $\neg(\varphi_1 \cup \varphi_2) \equiv (\neg \varphi_1) \ R(\neg \varphi_2)$ ,  $\neg(\varphi_1 \leftrightarrow \varphi_2) \equiv (\neg \varphi_1) \oplus (\neg \varphi_2)$ ,  $\varphi_1 \rightarrow \varphi_2 \equiv (\neg \varphi_1) \vee \varphi_2$ , etc.

**Theorem 2.2** (Etessami and Holzmann (2000); Babiak et al (2013)) *Any pure eventuality*  $\varphi$  *satisfies*  $\varphi \equiv F \varphi$ . *Any pure universality*  $\varphi$  *satisfies*  $\varphi \equiv G \varphi$ . *Any suspendable formula*  $\varphi$  *satisfies*  $\varphi \equiv G \varphi \equiv F \varphi \equiv X \varphi$ .

The sets of syntactic guarantee, syntactic safety, syntactic obligation formulas, syntactic recurrence formulas and syntactic persistence formulas are related to the temporal hierarchy of Manna and Pnueli (1990) in a way that has been discussed by Černá and Pelánek (2003). However, we first need to define automata before we can state those important results.

#### 2.3 Emerson-Lei Automata

It is a well-known result that Muller automata can recognize the set of all traces satisfying a given LTL formula and thus, may prove extremely useful in the synthesis process. *Emerson-Lei Automata* were defined (Emerson and Lei, 1987) and named (Safra and Vardi, 1989) in the 80s; they provide a way to describe a Muller acceptance condition using a positive Boolean formula over sets of states that must be visited finitely or infinitely often. Below we define the transition-based version of those automata, as used in the *Hanoi Omega-Automata Format* (Babiak et al, 2015). Instead of working directly with sets of transitions, we label transitions by multiple colored marks, as can be seen in Figure 3.

Let  $M = \{0, ..., n-1\}$  be a finite set of n contiguous integers called the set of *marks* or *colors*, from now on also written  $M = \{0, 1, ...\}$  in our examples. We define the set  $\mathcal{C}(M)$  of *acceptance formulas* according to the following grammar, where m stands for any mark in M:

$$\alpha ::= \top \mid \bot \mid \mathsf{Inf}(m) \mid \mathsf{Fin}(m) \mid \alpha \land \alpha \mid \alpha \lor \alpha$$

Acceptance formulas are interpreted over subsets of M. For  $N \subseteq M$  we define the satisfaction relation  $N \models \alpha$  inductively according to the following semantics:

$$N \models \top$$

,  $N \models \mathsf{Inf}(m)$  iff  $m \in N$ ,  $N \models \alpha_1 \land \alpha_2$  iff  $N \models \alpha_1$  and  $N \models \alpha_2$ ,  $N \not\models \bot$ ,  $N \models \mathsf{Fin}(m)$  iff  $m \notin N$ ,  $N \models \alpha_1 \lor \alpha_2$  iff  $N \models \alpha_1$  or  $N \models \alpha_2$ .

An Emerson-Lei automaton is an  $\omega$ -automaton labeled by marks whose acceptance condition is expressed as a positive Boolean formula on sets of marks that occur infinitely or finitely often in a run. More formally:

**Definition 4** (Transition-based Emerson-Lei Automata) A *transition-based Emerson-Lei automaton* (TELA) is a tuple  $\mathscr{A} = (Q, M, \Sigma, \delta, q_0, \alpha)$  where:

• Q is a finite set of states.

Table 1: Example of acceptance formulas for traditional acceptance conditions.

```

Büchi

Inf(\mathbf{0})

Inf(0) \wedge Inf(1) \wedge Inf(2) \wedge \dots

generalized Büchi

co-Büchi

Fin(\mathbf{0})

(\operatorname{Fin}(0) \wedge \operatorname{Inf}(1)) \vee (\operatorname{Fin}(2) \wedge \operatorname{Inf}(3)) \vee \dots

Rabin

(Inf(0) \lor Fin(1)) \land (Inf(2) \lor Fin(3)) \land \dots

Streett

Inf(0) \lor (Fin(1) \land (Inf(2) \lor (Fin(3) \land ...)))

parity min even

parity min odd

Fin(0) \wedge (Inf(1) \vee (Fin(2) \wedge (Inf(3) \vee ...)))

parity max even

(((Inf(0)) \land Fin(1))) \lor Inf(2)) \land Fin(3)) \lor \dots

(((\operatorname{Fin}(0)) \vee \operatorname{Inf}(1)) \wedge \operatorname{Fin}(2)) \vee \operatorname{Inf}(3)) \wedge \dots

parity max odd

```

- *M* is a finite set of marks.

- $\Sigma$  is a finite input alphabet.

- $\delta \subseteq Q \times \Sigma \times 2^M \times Q$  is a finite set of transitions.

- $q_0 \in Q$  is an initial state.

- $\alpha \in \mathscr{C}(M)$  is an acceptance formula.

Given a transition  $d=(q_1,\ell,A,q_2)\in \delta$ , we write  $d=q_1\overset{\ell,A}{\longrightarrow} q_2$ ;  $q_2$  is said to be a *successor* of  $q_1$ , and  $q_1$ , the *origin* of d. If  $A=\emptyset$ , the transition is said to be uncolored, and has no direct impact on the acceptance. A *run* r of  $\mathscr A$  is an infinite sequence of transitions  $r=(s_i\overset{\ell_i,A_i}{\longrightarrow} s_i')_{i\geq 0}$  in  $\delta^\omega$  such that  $s_0=q_0$  and  $\forall i\geq 0$ ,  $s_i'=s_{i+1}$ . Since  $\delta$  is finite, for any run r, there exists a position  $j_r\geq 0$  such that for each  $i\geq j_r$ , the transition  $s_i\overset{\ell_i,A_i}{\longrightarrow} s_i'$  occurs infinitely often in r. Let  $\mathsf{Rep}(r)=\bigcup_{i\geq j_r}A_i$  be the set of colors **rep**eated infinitely often in r.

A run r is *accepting* if  $\operatorname{Rep}(r) \models \alpha$ , and we then say that  $\mathscr A$  accepts the word  $(\ell_i)_{i \geq 0} \in \Sigma^{\omega}$ . We may then write  $r \models \alpha$ . The *language*  $\mathscr L(\mathscr A)$  is the set of words accepted by  $\mathscr A$ . Two TELA are *equivalent* if they have the same language. By extension, the language of a state  $q \in Q$  is the language of the automaton using q as initial state.

Finally, a TELA is *deterministic* if each state has at most one outgoing edge for any given letter, in other words,  $\forall (q,v) \in Q \times \Sigma$ ,  $|\{(s,\ell,A,d) \in \delta \mid s=q \land \ell=v\}| \leq 1$ , and it is *complete* if each state has at least one outgoing edge for any given letter, in other words,  $\forall (q,v) \in Q \times \Sigma$ ,  $|\{(s,\ell,A,d) \in \delta \mid s=q \land \ell=v\}| \geq 1$ .

The grammar of acceptance formulas can represent many traditional acceptance conditions, as illustrated in Table 1. For parity acceptance, interpreting the colors as numbers amounts to checking whether the minimum or maximum color seen infinitely often is odd or even.

Some subclasses of TELA are of specific interest to us. A *DELA* is a deterministic TELA. If it has parity acceptance, we call it *deterministic parity automaton* (DPA). ltlsynt works with *max odd* parity, but the techniques described can be adjusted to other types of parity acceptance. A *NBA* is a TELA with Büchi acceptance, and a *DBA* is the deterministic version.

The following theorem captures some well-established results linking LTL to TELA.

**Theorem 2.3** For any LTL formula there exists an equivalent NBA and an equivalent DPA. There exist some LTL formulas that cannot be represented by an equivalent DBA.

The following definition and theorem connect the syntactic obligation formula of Section 2.2 to the class of weak TELA:

**Definition 5** A *weak automaton* is a TELA in which all transitions that belong to the same strongly connected component have the same color. Without loss of expressivity, one can always recolor weak automata to use a Büchi acceptance condition Inf(0).

**Theorem 2.4** (Černá and Pelánek (2003); Dax et al (2007)) Any syntactic obligation formula can be converted into an equivalent deterministic weak automaton of minimal size.

Similarly, the classes of syntactic recurrence and syntactic persistence formula can be connected to specific types of deterministic automata.

**Theorem 2.5** (Černá and Pelánek (2003)) For any syntactic recurrence formula there exists an equivalent deterministic Büchi automaton and dually for any syntactic persistence formula there exists an equivalent deterministic co-Büchi automaton.

#### 2.4 Operations on Deterministic TELA

We now define operations over deterministic TELA that realize Boolean operations over their language. Let us first extend our definition of acceptance formulas via some syntactic sugar.

**Definition 6** (Syntactic sugar for acceptance formulas) Let  $\alpha$  be an acceptance formula, then  $\neg \alpha$  is the acceptance formula defined inductively by

$$\neg \top = \bot \qquad \neg \mathsf{Inf}(m) = \mathsf{Fin}(m) \qquad \neg (\alpha_1 \land \alpha_2) = (\neg \alpha_1) \lor (\neg \alpha_2)$$

$$\neg \bot = \top \qquad \neg \mathsf{Fin}(m) = \mathsf{Inf}(m) \qquad \neg (\alpha_1 \lor \alpha_2) = (\neg \alpha_1) \land (\neg \alpha_2)$$

For two acceptance formulas  $\alpha$  and  $\beta$ , let us define three additional operations:

$$\begin{split} \alpha &\to \beta = \neg \alpha \lor \beta \\ \alpha &\leftrightarrow \beta = (\alpha \land \beta) \lor (\neg \alpha \land \neg \beta) \\ \alpha &\oplus \beta = (\alpha \land \neg \beta) \lor (\neg \alpha \land \beta) \end{split}$$

**Theorem 2.6** (Complement of a deterministic TELA) Let  $\mathscr{A} = (Q, M, \Sigma, \delta, q_0, \alpha)$  be a deterministic complete TELA. We define  $\mathsf{Complement}(\mathscr{A})$  as the automaton  $(Q, M, \Sigma, \delta, q_0, \neg \alpha)$ , and we obviously have  $\mathscr{L}(\mathsf{Complement}(\mathscr{A})) = \mathscr{L}(\mathscr{A})^{\complement}$ .

**Theorem 2.7** (Generalized product) Let  $\mathscr{A}_1 = (Q_1, M_1, \Sigma, \delta_1, i_1, \alpha_1)$  and  $\mathscr{A}_2 = (Q_2, M_2, \Sigma, \delta_2, i_2, \alpha_2)$  be two deterministic TELA over the same alphabet using two disjoint sets of colors  $M_1$  and  $M_2$ .

*For any*  $\odot \in \{\land, \lor, \rightarrow, \leftrightarrow, \oplus\}$  *let*  $\mathsf{Product}_{\odot}(\mathscr{A}_1, \mathscr{A}_2)$  *be the TELA*  $(Q, M, \Sigma, \delta, i, \alpha)$  *where:*

- $Q=Q_1\times Q_2$ ,

- $\widetilde{\delta} = \{((s_1, s_2), \ell_1, m_1 \cup m_2, (d_1, d_2)) \mid (s_1, \ell_1, m_1, d_1) \in \delta_1, (s_2, \ell_2, m_2, d_2) \in \delta_2, \ell_1 = \ell_2\},$

- $i = (i_1, i_2),$

- $\alpha = \alpha_1 \odot \alpha_2$

Then, it follows that:

$$\begin{split} & \mathscr{L}(\mathsf{Product}_{\wedge}(\mathscr{A}_1,\mathscr{A}_2)) = \mathscr{L}(\mathscr{A}_1) \cap \mathscr{L}(\mathscr{A}_2) \\ & \mathscr{L}(\mathsf{Product}_{\vee}(\mathscr{A}_1,\mathscr{A}_2)) = \mathscr{L}(\mathscr{A}_1) \cup \mathscr{L}(\mathscr{A}_2) \\ & \mathscr{L}(\mathsf{Product}_{\rightarrow}(\mathscr{A}_1,\mathscr{A}_2)) = \mathscr{L}(\mathscr{A}_1)^{\complement} \cup \mathscr{L}(\mathscr{A}_2) \\ & \mathscr{L}(\mathsf{Product}_{\leftrightarrow}(\mathscr{A}_1,\mathscr{A}_2)) = (\mathscr{L}(\mathscr{A}_1) \cap \mathscr{L}(\mathscr{A}_2)) \cup (\mathscr{L}(\mathscr{A}_1)^{\complement} \cap \mathscr{L}(\mathscr{A}_2))^{\complement} \\ & \mathscr{L}(\mathsf{Product}_{\oplus}(\mathscr{A}_1,\mathscr{A}_2)) = (\mathscr{L}(\mathscr{A}_1) \smallsetminus \mathscr{L}(\mathscr{A}_2)) \cup (\mathscr{L}(\mathscr{A}_2) \smallsetminus \mathscr{L}(\mathscr{A}_1)) \end{split}$$

The above product can be adapted to the case where the set of colors  $M_1$  and  $M_2$  used by each automaton are not disjoint, by first renumbering the colors of one automaton to make sure they are unique. In the end, the number of colors used by the above product is  $|M_1| + |M_2|$ .

In the context of reactive synthesis, we will consider an alphabet  $\Sigma = \mathbb{B}^{I \cup O}$ . The edges of a TELA are labeled by input and output propositions.

#### 2.5 Parity Games

We view parity games as specialized versions of TELA where each state is owned by one of two players.

**Definition 7** (Parity Game) A *parity game* is a TELA of the form  $\mathscr{G} = (Q_0 \cup Q_1, M, \Sigma, \delta, q_0, \alpha)$  such that:

- $Q_0$  and  $Q_1$  are two *disjoint* sets of states respectively controlled by player 0 ("the environment") and player 1 ("the controller").

- $\alpha$  is a parity max odd condition.

A run of  $\mathscr{G}$  is called a *play*; it is said to be *winning* for player 1 if it is an accepting run, otherwise, if the run is non-accepting, it is winning for player 0.

As shown in Figure 3, states in  $Q_0$  will be denoted  $\bigcirc$ , and states in  $Q_1$ ,  $\diamondsuit$ . Intuitively, player 0 and player 1 take turns and pick a successor in accordance to the current state and the transitions defined in  $\delta$ . Player 1 tries to ensure that the resulting run is accepting, while player 0 is actively preventing this outcome.

A *memoryless strategy* for a player X (with  $X \in \{0,1\}$ ) is a function  $\sigma_X : Q_X \to \delta$  such that  $\sigma_X(q)$  is always an outgoing transition of  $q \in Q_X$ .

A play  $p = (s_i \xrightarrow{\ell_i, A_i} s_i')_{i \geq 0}$  is said to be *consistent* with  $\sigma_X$  if  $\forall s_i \in Q_X$ ,  $(s_i \xrightarrow{\ell_i, A_i} s_i') = \sigma_X(s_i)$ , that is, the transition leaving any state in  $Q_X$  in that run is determined by  $\sigma_X$ . Finally,  $\sigma_X$  is said to be a *winning strategy* for player X if any play that is starting in  $q_0$  and consistent with  $\sigma_X$  is winning for player X.

Parity games are known to be *positionally determined*, this means that one of the two players has a memoryless winning strategy. Büchi games are *positionally determined* too, however as seen in Theorem 2.3, DBA are less expressive than DPA; we therefore focus on DPA. Several algorithms exist for finding winning strategies in parity games (Zielonka, 1998; Jurdziński, 2000; van Dijk, 2018), and those that are defined with state-based acceptance can easily be adapted to transition-based acceptance. Our implementation is based on Zielonka's algorithm with improvements taken from van Dijk (2018).

#### 2.6 Mealy Machines

Reactive controllers produce for an input stream of Boolean valuations a matching output stream. We model this behavior thanks to a common finite state model known as *Mealy machines*, as shown in Figure 5. In particular, we will use Mealy machines to represent the winning strategies we obtain while solving parity games. However, a given specification may yield multiple compatible output valuations for a given input: our model must therefore account for this peculiarity of reactive synthesis.

**Definition 8** An *Incompletely specified Generalized Mealy Machine* (IGMM) is a tuple  $M = (I, O, Q, q_{init}, \delta, \lambda)$ , where I is a set of *input propositions*, O a set of *output propositions*, O a finite set of *states*, O an *initial state*, O and O are the O and O and O are the O are the O are the O and O are the O are the O are the O and O are the O are

It is worth noting that the transition function is *input-deterministic* but not complete with regards to Q as  $\delta(q,i)$  could be undefined. (When  $\delta(q,i)$  is undefined, the Mealy machine will be free to do anything, hence the convention that  $\lambda(q,i) = \top$ .) Furthermore, the output function may return a set of valuations for a given input valuation and state. This is not an unexpected definition from a reactive synthesis point of view, as discussed earlier.

**Definition 9** (Semantics of IGMMs) Let  $M=(I,O,Q,q_{init},\delta,\lambda)$  be an IGMM. For all  $u\in\mathbb{B}^I$  and  $q\in Q$ , if  $\delta(q,u)$  is defined, we write that  $q\xrightarrow{u/v}\delta(q,u)$  for all  $v\in\lambda(q,u)$ . Given two infinite sequences of valuations  $\iota=i_0\cdot i_1\cdot i_2\cdots\in(\mathbb{B}^I)^\omega$  and  $o=o_0\cdot o_1\cdot o_2\cdots\in(\mathbb{B}^O)^\omega$ , we note  $(\iota,o)\models M_q$  if and only if:

- either there is an infinite sequence of states  $(q_j)_{j\geq 0} \in Q^{\omega}$  such that  $q=q_0$  and  $q_0 \xrightarrow{i_0/o_0} q_1 \xrightarrow{i_1/o_1} q_2 \xrightarrow{i_2/o_2} \cdots;$

- or there is a finite sequence of states  $(q_j)_{0 \le j \le k} \in \mathcal{Q}^{k+1}$  such that  $q = q_0$ ,  $\delta(q_k, i_k)$  is undefined, and  $q_0 \xrightarrow{i_0/o_0} q_1 \xrightarrow{i_1/o_1} \cdots q_k$ .

We then say that starting from state q, M produces output o given the input t.

Note that if  $\delta(q_k, i_k)$  is undefined, the machine is allowed to produce an arbitrary output from then on. Furthermore, given an input word  $\iota$ , there is always at

least one output word o such that  $(\iota, o) \models M_q$  but there might be more. Eventually, when that machine is encoded into a circuit, we will have to settle on a single output word per input word, but in the meantime, this additional flexibility can be used for simplification.

**Definition 10** (Realizability of an LTL formula by an IGMM) Let I and O be two disjoint sets of input and output propositions. Given two sequences  $t = i_0 \cdot i_1 \cdot i_2 \cdots \in (\mathbb{B}^I)^{\omega}$  and  $o = o_0 \cdot o_1 \cdot o_2 \cdots \in (\mathbb{B}^O)^{\omega}$ , we denote by  $t \wedge o$  the sequence  $(i_0 \wedge o_0) \cdot (i_1 \wedge o_1) \cdot (i_2 \wedge o_2) \cdots \in \mathbb{B}^{O \cup I}$ .

Let  $\varphi$  be an LTL formula built upon  $I \cup O$ . We say that an IGMM  $M = (I, O, Q, q_{init}, \delta, \lambda)$  realizes the specification  $\varphi$  if for any pair of sequences  $\iota \in (\mathbb{B}^I)^{\omega}$  and  $o \in (\mathbb{B}^O)^{\omega}$ , we have

$$(\iota, o) \models M_{q_{init}} \implies \iota \land o \models \varphi$$

We say that a specification  $\varphi$  is *realizable* if there exists an IGMM that realizes it.

In other words, the machine M realizes the specification  $\varphi$  if, regardless of the provided input  $\iota$ , any output sequence o that M may produce will (together with  $\iota$ ) satisfy  $\varphi$ .

**Definition 11** (Variation and specialization) Let  $M = (I, O, Q, q_{init}, \delta, \lambda)$  and  $M' = (I, O, Q', q'_{init}, \delta', \lambda')$  be two IGMMs. Given two states  $q \in Q$ ,  $q' \in Q'$ , we say that q' is a *variation* of q if  $\forall \iota \in (\mathbb{B}^I)^{\omega}$ ,  $\{o \mid (\iota, o) \models M'_{q'}\} \cap \{o \mid (\iota, o) \models M_q\} \neq \emptyset$ ; and q' is a *specialization* of q if  $\forall \iota \in (\mathbb{B}^I)^{\omega}$ ,  $\{o \mid (\iota, o) \models M'_{q'}\} \subseteq \{o \mid (\iota, o) \models M_q\}$ . We say that M' is a variation (resp. specialization) of M if  $q'_{init}$  is a variation (resp. specialization) of  $q_{init}$ .

Intuitively, all the input-output pairs accepted by a specialization q' in M' are also accepted by q in M. Therefore, if  $M_q$  realizes a specification  $\varphi$ , then its specialization  $M'_{q'}$  also realizes  $\varphi$ . Figure 6 shows a specialization of Figure 5. This specialization relation can obviously be used to compute smaller machines that still comply with a given specification.

Finally, in order for two states to be a variation of one another, for all possible inputs they must be able to agree on a common output behavior. This property can be used to reduce the number of states in a given machine; however, additional care has to be taken as we will show in Section 4.

## 2.7 The LTL Reactive Synthesis Problem

The LTL Reactive Synthesis problem can be formulated as follow: given an LTL formula  $\varphi$  over a set of variable  $O \cup I$  partionned as input and output, does there exist an IGMM M that realizes  $\varphi$ ?

This is the problem posed by SYNTCOMP (Jacobs et al, 2017, 2019), the annual Reactive synthesis competition, which distinguishes two subproblems:

- in the *realizability* track, the goal is simply to decide the above question without providing *M*;

- in the *synthesis* track, the goal is to construct a reactive controller that realizes the specification, or to state that the specification is not realizable.

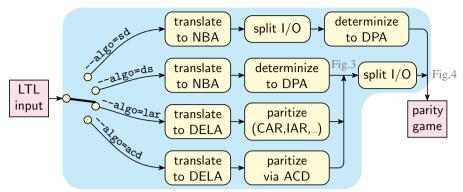

**Fig. 8**: Zoom on the block "translate  $\varphi_i$  to game" from Fig. 7. The --algo option of ltlsynt will select one of several ways to construct a parity game.

In the latter track, the controller has to be constructed as an AIG circuit expressed in the AIGER format (Biere, 2007). Section 5 will be devoted to the transformation of IGMM into AIG circuits.

# 3 Translating LTL Formulas into Games

#### 3.1 Different Approaches

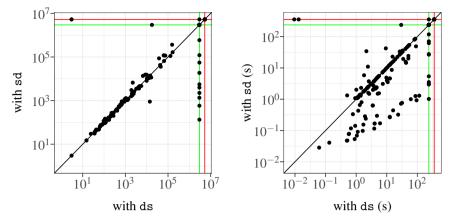

Figure 8 shows four approaches for transforming an LTL formula into a parity game. In ltlsvnt, these approaches can be selected using the --algo option.

The ds branch corresponds to the straightforward approach described in the introduction. The formula is first converted into a non-deterministic Büchi automaton using Spot's standard translation (Duret-Lutz, 2014). Then it is determinized into a parity automaton with a variant of Safra's determinization (Redziejowski, 2012). The result, which may look like Fig. 3 is then converted into a game as in Fig. 4 by splitting transitions of the form  $\underbrace{i_1i_2o_1o_2}_{i_1i_2o_1o_2}$  into  $\underbrace{i_1i_2}_{o_1o_2}$ . By ensuring that at most one intermediate state is created per input valuation, determinism is preserved (as discussed in Section 3.3). The game is also made input-complete, to ensure that the environment can freely chose among all input valuations.

The sd approach is similar, except that the split is performed before the determinization. This slightly counter-intuitive order is motivated by the fact that at a given time, the determinization then has to deal only with valuations in  $2^O$  or valuations in  $2^I$ , while in the previous approach, it had to cope with  $2^{O \cup I}$  valuations.

The other two approaches are attempts to reduce the costs of obtaining a DPA. This is done by first converting the formula into a deterministic TELA (*DELA*), i.e., using arbitrary acceptance condition, and then converting this automaton into a DPA. The conversion to deterministic TELA is described in the next section. The two approaches differ in how the *paritization* (i.e., the conversion of the TELA to a parity automaton) is done.

The lar approach uses a paritization procedure based on *latest appearance* records with many improvements described in previous work (Renkin et al, 2020).

#### Algorithm 1 Translation of an LTL formula into a deterministic EL-automaton.

```

1: Input: An LTL formula \varphi in NNF, and an optional binary operator op.

2: Output: A deterministic EL-automaton.

3: function ToDELA(\varphi, op = \bot)

if \varphi matches XX...X \alpha then

4:

i copies of X

\mathscr{A}_{\alpha} \leftarrow \mathsf{ToDELA}(\alpha)

5:

create \mathscr{A}_{\varphi} from \mathscr{A}_{\alpha} by prepending i states in the obvious way

6:

return \mathscr{A}_{\sigma}

7:

if \varphi matches f_1 \odot \cdots \odot f_n for \odot \in \{\land, \lor, \leftrightarrow, \oplus\} \setminus \{op\} and n \ge 2 then

8:

Partition \{f_1,...,f_n\} as S \cup O \cup R with \begin{cases} S: suspendable formulas \\ O: obligation formulas \\ R: anything else \end{cases}

9:

\mathscr{A} \leftarrow \mathsf{Product}_{\odot}(\mathsf{ToDELA}(\bigcirc_{f \in R} f, \bigcirc), \mathsf{BuildMinWDBA}(\bigcirc_{f \in O} f))

10:

for s \in S do

11:

\mathscr{A} \leftarrow \mathsf{ProductSusp}_{\odot}(\mathscr{A}, \mathsf{ToDELA}(s, \odot))

12:

return A

13:

if \varphi is a syntactic obligation then

14:

return BuildMinWDBA(\varphi)

15:

if \varphi matches G(\Lambda_i F \alpha_i) where \alpha_i are syntactic guarantees then

16:

return GFGuaranteeToDBA(\varphi)

17:

if \varphi matches F(\bigvee_i G\alpha_i) where \alpha_i are syntactic safeties then

18:

return Complement(GFGuaranteeToDBA(\neg \phi))

19:

return Determinize(ToNBA(\varphi))

20:

```

The newest acd approach replaces the above paritization by one based on the *Alternating Cycle Decomposition* (ACD) (Casares et al, 2021, 2022). It is guaranteed to produce automata that are at most as big as lar.

#### 3.2 From LTL to Deterministic TELA

There exist a number of tools, such as delag (Müller and Sickert, 2017) or ltl3tela (Major et al, 2019) for transforming LTL formulas into deterministic TELA (DELA). Spot's own built-in procedure for this purpose, used by ltlsynt, is inspired from delag.

Algorithm 1 shows a slightly simplified view of how Spot translates  $\varphi$  into a deterministic TELA. Formula  $\varphi$  is assumed to be in a negative normal form (i.e.,  $\neg$  have been pushed down in front of the atomic propositions, and implications have been rewritten away, as in Theorem 2.1) where equivalence  $(\leftrightarrow)$  and xor  $(\oplus)$  can still be used.

It builds upon the following procedures:

- Product $_{\odot}$  builds a product of two deterministic automata using a standard synchronous product, and combines their acceptance conditions using  $\odot \in \{\land, \lor, \leftrightarrow, \oplus\}$  (see Theorem 2.7).

- ProductSusp $_{\odot}$  also builds a product, but assumes the second argument is a suspendable property. As a consequence, the actual product needs only to be performed in the accepting SCCs of the first automaton. This construction is similar to constructions discussed by Müller and Sickert (2017) and Babiak et al (2013), and is justified by Theorem 2.2.

- BuildMinWDBA transforms any obligation formula into a minimal weak deterministic Büchi automaton using a procedure described by Dax et al (2007).

- GFGuaranteeToDBA is an algorithm inspired from a similar one by Esparza et al (2018) and discussed in more details later. It can convert any formula of the form  $G(\Lambda_i F \alpha_i)$ , where  $\alpha_i$ s are syntactic guarantee formulas, into a deterministic Büchi automaton.

- Complement dualizes the acceptance condition of any deterministic TELA to complement it (see Theorem 2.6).

- ToNBA converts an LTL formula into a non-deterministic Büchi automaton. (Duret-Lutz, 2014)

- Determinize determinizes a non-deterministic automaton into a parity automaton, using a Safra-based algorithm. Spot implements Redziejowski's algorithm (2012).

Let us explain this algorithm by starting on line 20, which is the only necessary line. It is well known that (1) any LTL formula can be converted into a non-deterministic Büchi automaton with an exponential blowup, (2) not all LTL formulas may be represented as deterministic Büchi automaton. As a consequence, applications that require deterministic automata usually rely on more complex acceptance conditions. For instance there exists procedures for transforming non-deterministic Büchi automata (NBA) into deterministic Rabin automata or into deterministic parity automata (DPA), and those also have exponential blowups. Line 20 uses such a determinization to obtain a DPA from an LTL translation, at the cost of a doubly-exponential construction in the worst case (Kupferman and Rosenberg, 2010).

The other lines are therefore here to help reduce the cost of this construction, by providing specialized constructions for certain subclasses of formulas, and by decomposing the formula into smaller parts that are cheaper to translate and later recompose.

The idea behind the decomposition is that if a formula  $\varphi$  has the shape  $f_1 \odot \cdots \odot f_n$ , for some Boolean operator  $\odot \in \{\lor, \land, \leftrightarrow, \oplus\}$ , then the deterministic TELA  $\mathscr{A}_{\varphi}$  can be obtained by making a synchronous product of the deterministic TELA  $A_{f_i}$  obtained for each  $f_i$ , using operator  $\odot$  to combine the acceptance conditions. In this process, the translation of the smaller  $f_i$  might use more specialized algorithms. If more specialized algorithms are not available, empirical experiences tell us that it is usually best to translate  $\varphi$  without decomposing it, because the complexity of the translation is mostly proportional to the size of the produced automata anyway.

It is important to be able to decompose on  $\leftrightarrow$  and  $\oplus$  and not just  $\land$  and  $\lor$ . The reason is that  $\leftrightarrow$  in particular often occurs in synthesis specifications, and translating  $f \leftrightarrow g$  as  $\mathsf{Product}_{\odot}(\mathscr{A}_f, \mathscr{A}_g)$  involves only one product, while the equivalent formula  $(f \land g) \lor (\neg f \land \neg g)$  would require three products. The same reduction in number of products is achieved for  $\oplus$ , but would not be obtained for  $\to$ . Hence we are happy to assume implications have been removed when the input formula was rewritten in negative normal form.

This idea of decomposing the LTL formula to call specialized constructions is similar to that used in the tool delag (Müller and Sickert, 2017). In delag, a formula is split into syntactic safety, syntactic guarantee, another class called *fairness*, and anything else. We generalize this slightly by using using syntactic obligations (a super-class of syntactic safety and syntactic guarantee), suspendable formulas (a super-class of delag's *fairness* class), and anything else. The partition into these three classes is done on lines 8–9.

Several operations occur on line 10. Then, all formulas of set R, which do not belong to a subclass for which we have a dedicated construction, are translated recursively with ToDELA( $\bigcirc_{f \in R} f$ ,  $\odot$ ). The reason for the recursion, as opposed to calling Determinize(ToNBA( $\bigcirc_{f \in R} f$ )) directly, is that if R contains a single formula whose top-level operator is a Boolean operator different from  $\odot$ , it might be decomposed again.

Similarly, all formulas of set O, are translated into a minimal weak deterministic Büchi automaton following a technique of Dax et al (2007); essentially, for a syntactic obligation formula  $\alpha$ , the following steps, which are embodied in the BuildMinWDBA function, produce a minimal WDBA (Theorem 2.4):

- 1. translate  $\alpha$  into an NBA  $N_{\alpha}$ ,

- 2. ignoring accepting states, use the powerset construction on  $N_{\alpha}$  to obtain the deterministic structure  $D_{\alpha}$ ,

- 3. any SCC of  $D_{\alpha}$  that intersects an accepting SCC of  $N_{\alpha}$  in the synchronous product of  $N_{\alpha} \otimes D_{\alpha}$  should be marked as accepting

- 4. now  $D_{\alpha}$  is a weak deterministic automaton for  $\alpha$ , and it can be minimized using Löding's algorithm (2001).

The automata resulting from the translations of  $\bigcirc_{f \in R} f$  and  $\bigcirc_{f \in O} f$  are then composed by taking their product (we are still on line 10). (For simplicity we assume here that if O or R is empty, its translation gives a simple universal automaton. But the implementation of course skips the product in this case.) Spot's implementation of Product $_{\odot}$  has an extra trick, used here: when one of the operand is a weak automaton, it does not need to contribute colors to the resulting product.

Lines 11–12 integrate the suspendable formulas to the result one after the other, by translating them recursively, and then using the ProductSusp<sub>O</sub> method.

When the ToDELA function is called, the input formula has generally been simplified using folklore rewritings such a changing  $(Xf_1) \odot (Xf_2)$  into  $X(f_1 \odot f_2)$ . For this reason, lines 4–7 strip any leading Xs in order to apply the construction to the rest of the formula.

**Fig. 9**: (a) a DBA for  $F(a \leftrightarrow Xa)$ ; (b,c,d) three DBAs for  $GF(a \leftrightarrow Xa)$ .

Finally, lines 14–19 detect subclasses of formulas for which a specialized construction exists. If  $\varphi$  is a syntactic obligation, the aforementioned BuildMinWDBA function is used.

If formula  $\varphi$  has the form  $G(\bigwedge_i F\alpha_i)$ , and  $\alpha_i$  is a syntactic guarantee formula, then the following algorithm from Esparza et al (2018) can be used:

- 1. Translate  $\bigwedge_i F\alpha_i$  into a DBA *A* with a single accepting state that is terminal. The simple structure of  $\bigwedge_i F\alpha_i$  makes this possible. (Fig. 9(a) gives an example.)

- 2. Build  $A_{\varphi}$  from A by redirecting the loop of the accepting states to the initial state. (Fig. 9(b).)

Our implementation of GFGuaranteeToDBA improves upon the above by redirecting not the outgoing transition of the accepting states, but its incoming transitions (Fig. 9(c)): for each transition going to the terminal state, pretend that this letter is read from the initial state to pick the new destination. If such a transition is necessarily preceded by some forced sequence of valuations, any suffix of this sequence of valuations can actually be replayed from the initial state, allowing tighter loops. Finally, note that state 0 and 1 of Fig. 9(c) have the same successors, so they can be merged to obtain the automaton Fig. 9(d).

# 3.3 Splitting Automata

Once a parity automaton has been obtained (as in Fig. 3), we split its transitions to separate input signals from output signals, and obtain a parity game (as in Fig. 4). In this game player 1 ("the controller") selects the output valuations and can effectively react to the input valuations selected by player 0 ("the environment").

On the --algo=sd path of Fig. 8, we apply this split operation to non-deterministic Büchi automata. Therefore, below, we define it for any acceptance condition, and partition the states of the resulting automaton as  $Q_0 \cup Q_1$ , with  $Q_{0/1}$  being the set of states belonging to player 0/1, allowing this automaton to be interpreted as a game if desired.

**Definition 12** (Splitting an Emerson-Lei Automata) Let  $\mathscr{A} = (Q, M, \mathbb{B}^{I \cup O}, \delta, q_0, \alpha)$  be a TELA. The *split* of  $\mathscr{A}$  is the TELA  $\mathscr{A}_s = (Q_0 \cup Q_1, M, \mathbb{B}^I \cup \mathbb{B}^O, \delta_0 \cup \delta_1, q_0, \alpha)$ , where:

- $Q_0 = Q$ ,

- $Q_1 = Q \times \mathbb{B}^I$ ,

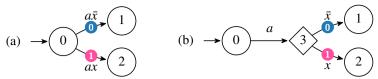

**Fig. 10**: (a) Original automaton with  $I = \{a\}$  and  $O = \{x\}$ . (b) Split automaton interpreted as a game with  $Q_0$  as round states, and  $Q_1$  as diamonds states.

$$\bullet \ \, \delta_0 = \Big\{ s \xrightarrow{\ell_i, \emptyset} (s, \ell_i) \, \Big| \, \ell_i \in \mathbb{B}^I, \ell_o \in \mathbb{B}^O, s \xrightarrow{\ell, A} d \in \delta, \ell = \ell_i \wedge \ell_o \Big\}, \\ \bullet \ \, \delta_1 = \Big\{ (s, \ell_i) \xrightarrow{\ell_o, A} d \, \Big| \, \ell_i \in \mathbb{B}^I, \ell_o \in \mathbb{B}^O, s \xrightarrow{\ell, A} d \in \delta, \ell = \ell_i \wedge \ell_o \Big\}.$$

Figure 10 shows a small example demonstrating how edges with identical inputs are fused into a single edge for the environment player. This ensures that states in  $Q_0$  are always deterministic, while states in  $Q_1$  are only deterministic if the input TELA is deterministic.

In a similar manner to transitions, we can split runs: if  $r \in (\mathbb{B}^{I \cup O})^{\omega}$ ,  $r = (r_i)_{i \geq 0}$ , and we consider  $\forall i \geq 0$ ,  $r_i = r_i^I r_i^O$  where  $r_i^I \in \mathbb{B}^I$  and  $r_i^O \in \mathbb{B}^O$  are again the respective projections of  $r_i$ . Then the split of r is the run  $r_s = r_0^I r_0^O r_1^I r_1^O \dots$  in  $(\mathbb{B}^I \cdot \mathbb{B}^O)^{\omega}$ . Obviously,  $\mathscr{A}$  accepts a run r if and only if  $\mathscr{A}_s$  accepts  $r_s$ : splitting a TELA preserves the underlying specification as a game.

#### **Two Implementation Details**

The definition of TELA and game used here are deliberately simplified concepts to ease the notations. In particular, our implementation of TELA labels transitions with subsets of valuations (i.e., arbitrary Boolean formulas over  $I \cup O$ ) instead of only one valuation at a time, in order to reduce the number of transitions stored and iterated upon. The splitting procedure detailed above is easily adapted to this setting: using subsets of valuations as  $\ell_i$  in  $(s, \ell_i)$  will also help reduce the size of  $Q_1$ .

Furthermore, if the acceptance condition is *parity max odd*, the transitions introduced in  $\delta_0$  can be colored using the minimal color used in the outgoing transitions of their destination states (with no acceptance mark being considered smaller than any color). For instance if the automaton of Fig 10(b) has *parity max odd* acceptance, the transition between states 0 and 3 can be colored with ①, the minimum color seen in the outgoing transitions of 3.

# 4 Simplifying Winning Strategies using Generalized Mealy Machines

Once a winning strategy for player 1 has been found for a game, we extract it as an Incompletely specified Generalized Mealy Machine. This is done in a simple way: first every outgoing edge of a state in  $Q_1$  that is not part of the strategy is removed, as well as all colors. Then the reachable part of the remaining automaton can be seen as a collection of pairs of transitions of the form  $O(10^{1/2})$  which we fuse back

into  $\underbrace{i_1i_2/o_1o_2}$  to obtain a Mealy machine. For instance the Mealy machine in Fig. 5 is obtained from the game together with the strategy highlighted by the thick transitions in Fig. 4 using this approach.

These Mealy machines will then be encoded into And-Inverter Graphs as we discuss in Section 5, but first they can be simplified.

If a Mealy machine has n states, the AIG will use  $\lceil \log n \rceil$  latches to remember its current state; and reducing this number will usually reduce the size of the AIG (but that is not always true). For instance the Mealy machine in Fig. 5 requires two latches (two bits are needed to distinguish the three states), while the one of Fig. 6 requires only one latch (as shown in Fig. 2).

As shown in Fig. 4, a strategy determines for each state which transition to choose. As transitions are labeled by arbitrary sets of valuations (over the output propositions), the strategy implicitly defines a set of valid output valuations to respond to the last input valuation. The controller is free to pick any one of these valuations and is guaranteed to respect the initial specification.

This brings us back to the notion of specialization of Mealy machines, introduced in Section 2.6. Please recall that intuitively, a Mealy machine  $\mathcal{M}_1$  is a specialization of a Mealy machine  $\mathcal{M}_2$  if for any input sequence, any associated output produced by  $\mathcal{M}_1$  can also be produced by  $\mathcal{M}_2$ .

Our goal is to derive a specialization of a given Mealy machine having fewer states. In the following subsections, we give an overview of two ways to perform such a reduction: in the first one, called *minimization*, we seek to obtain the specialization having the fewest states possible. In the second one, called *reduction*, we seek to reduce the number of states of the machine, without necessarily achieving the optimal result. The later reduction is motivated by the high computational complexity of the minimization: the problem is known to be NP-complete (Pfleeger, 1973).

These two simplifications are further detailed in a previous work (Renkin et al, 2022), so we only provide intuitions here.

#### 4.1 SAT-Based Minimization of IGMM

Here we discuss a minimization procedure based on the approach presented by Abel and Reineke (2015). Besides improving their algorithm on several points, we generalize this approach to our strictly more expressive Mealy machine model IGMM.

If the Mealy machine was completely specified, we would minimize it by computing a quotient of equivalent states. However, the freedom we get from the incomplete specification allows some of the states to belong to several classes of that equivalence relation, depending on how we decide to specialize those states. To capture this notion of group of compatible states, we define variation classes, and require three additional properties: variation classes have to cover the entire automaton, they have to behave similarly with respect to their successor classes and their possible output.

**Definition 13** (Variation class) Given an IGMM  $M = (I, O, Q, q_{\text{init}}, \delta, \lambda)$ , a *variation class*  $C \subseteq Q$  is a set of states, such that all elements are pair-wise variations (See Def. 11). That is

Fig. 11: Minimization example

$\forall q, q' \in C, q'$  is a variation of q. In the remainder of this section, we will call a variation class simply class as there is no ambiguity.

Note that variation classes should not be mistaken for equivalence classes, since being a variation is not an equivalence relation.

**Definition 14** (Cover condition) We say that a set of classes S covers the machine M if every state of M appears in at least one class.

**Definition 15** (Closure condition) We say a set of classes S is closed if for all  $C_j \in S$  and for all input  $i \in \mathbb{B}^I$  there exists a class  $C_k \in S$  such that for every state q of  $C_j$  we have either  $\delta(q,i) \in C_k$  or  $\delta(q,i)$  is undefined.

**Definition 16** (Nonemptiness condition) We say that a class C has a nonempty output if  $\bigcap_{q \in C} \lambda(q, i)$  is not empty for all input  $i \in \mathbb{B}^I$ .

A set of classes that satisfies the three previously described conditions gives rise to a specialization of the original machine. Therefore, finding the minimal number of classes able to satisfy the conditions amounts to finding the minimal specialization.

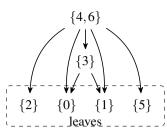

For instance in Figure 11a, colors are used to represent three variation classes that satisfy the three additional constraints. (States 4 and 6 belong to the three classes.) The minimal corresponding IGMM is the one of Figure 11b.

In order to find such a decomposition, we fix the number of classes n and encode the conditions given above as a SAT problem. Once we have found the smallest n for which a satisfying assignment has been found by a SAT solver, we can extract the minimal IGMM from it.

A basic iterative algorithm would be to ask if the conditions can be satisfied with one class, and if not, increase the number of classes by one. This naive approach can be improved as shown in Algorithm 2 by first computing a lower bound on the number of classes necessary: for each pair of states q and q', we test if they are variations of one another. If not, these two states cannot be in the same class. We

#### Algorithm 2 SAT-based minimization

```

1: bool \cap mat \leftarrow is Not Variation Of (M)

> Computing the variation matrix

2: set P \leftarrow \text{extractPartialSol(mat)}

Description Descr

3: clauses ← empty list

4: for n \leftarrow |P| to |Q| - 1 do

▷ Using the lower bound inferred from P

addCoverCondition(clauses, M, P, mat, n)

5:

addClosureCondition(clauses, M, P, mat, n)

6:

(sat. solution) \leftarrow satSolver(clauses)

Solving cover & closure cond.

7:

while sat do

8:

if verifyNonEmpty(M, solution) then

9:

return buildMachine(M, solution)

10:

addNonemptinessCondition(clauses, M, solution)

11:

(sat. solution) \leftarrow satSolver(clauses)

12.

► If no solution has been found, return M

return copyMachine(M)

```

therefore compute a set of states such that no two states in the set are variations of one another. The size of this set gives us a lower bound on the number of classes necessary.

#### 4.2 Bisimulation-based Reductions

Our second approach relies on an adaptation of a procedure called bisimulation (Babiak et al, 2013) used to reduce the size of an  $\omega$ -automaton. Again, describing the method in detail is beyond the scope of this paper because this work has been previously published (Renkin et al, 2022); however, we would like to share some insights about how this transformation works. This procedure uses as an intermediate step an association between a state of the automaton and a Boolean formula called *signature*. This signature is computed iteratively in such a way that two states with the same signature recognize the same language. We will now present two algorithms based on an adaptation of this signature-based approach that seeks to reduce an IGMM.

#### 4.2.1 Bisimulation Reduction

**Definition 17** (Bisimilarity) Two states q and q' are *bisimilar* if q is a specialization of q' and q' is a specialization of q.

For instance states 4 and 6 in Figure 11a are bisimilar. We can therefore replace the edge that goes from 3 to 6 by an edge that goes from 3 to 4, thereby obtaining a machine with 6 states.

Generally, the *bisimulation reduction* of an automaton is the quotient of that automaton with respect to the above bisimilarity relation. However, this reduction does not take any advantage of the flexibility provided by an IGMM.

**Fig. 12**: Specialization graph of the IGMM of Fig. 11a

| q | i             | r(q) |

|---|---------------|------|

| 0 | $\rightarrow$ | 0    |

| 1 | $\rightarrow$ | 1    |

| 2 | $\rightarrow$ | 2    |

| 3 | $\rightarrow$ | 1    |

| 4 | $\rightarrow$ | 1    |

| 5 | $\rightarrow$ | 5    |

| 6 | $\rightarrow$ | 1    |

**Fig. 13**: Chosen representative mapping.

**Fig. 14**: IGMM obtained by reducing that of Fig. 11a

#### 4.2.2 Bisimulation Reduction with Output Assignment

In order to merge more states, we introduce an additional preprocessing step called "output assignment." Consider that we have two states q and q' such that for every input sequence, any output that can be associated to a run starting at q can also be produced when starting at q'. If q and q' are not bisimilar, it means that a run starting at q' can produce a larger set of output sequences than a run starting in q for the same input sequence. By restricting what can be produced from q' to match what is produced from q, we have effectively made them bisimilar and they can therefore be merged using the approach described above. Note that as we restrict the outputs from q', the resulting machine is a specialization of the original one.

To achieve this, we introduce a specialization relation based on the signature. This relation shown in Figure 12 gives us a relation of specialization between states. In this example, state 0 is a specialization of states 3, 4 and 6. The main idea is to associate to each state a state that specializes it. It gives us a representative function given in Figure 13. Once this representative function is found we restrict the output of each state to match the output given by the representative function (i.e.,  $\lambda(q,i) = \lambda(r(q),i)$ ). The resulting specialization of the original IGMM can then be reduced by bisimulation (Fig. 14). Note that this procedure produces a machine with as many states as leaves in the specialization tree.

# 5 Encoding Generalized Mealy Machines as And-Inverter Graphs

The final step in our pipeline is to encode the obtained Mealy machine as an And-Inverter Graph (AIG). And-Inverter Graphs are a special type of directed acyclic graph which is widely used in logic synthesis (Mishchenko et al, 2006; Brayton and Mishchenko, 2010) either as the final circuit or as an intermediate representation before further optimizations. The most common format to represent such circuits is called *AIGER* (Biere, 2007), which is also the output format used in the synthesistracks of SYNTCOMP (Jacobs et al, 2017, 2019).

As previously mentioned, AIGs correspond to circuits built from *and gates* with exactly two inputs \_\_\_, *negations* o which can appear on edges and negate the signal if present, and *latches* \_\_\_\_ that delay their input by one tick, and output 0 initially.

The input corresponds to an Incompletely specified Generalized Mealy Machine which we want to encode as AIG. Note that the actual behavior of the AIG only needs to correspond to a specialization of the input machine. Recall that the output function for IGMMs is defined as  $\lambda: (Q, \mathbb{B}^I) \to 2^{\mathbb{B}^O} \setminus \{\emptyset\}$ . This means that for a given state and input valuation  $\mathbb{B}^I$  there possibly exist multiple output valuations in  $\mathbb{B}^O$  compatible with the specification. Such non-determinism can however not be expressed by a logical circuit, and we therefore need to choose one of the possible valuations, causing the encoded machine to be a specialization of the input machine. We use a function called ChooseOneValuation to resolve these choices when we do not have further constraints. This function takes an output label  $L \in 2^{\mathbb{B}^O} \setminus \{\emptyset\}$  and returns a valuation  $o \in \mathbb{B}^O$  such that  $o \in L$ . (Our implementation attempts to select some o that maximizes the number of do-not-care variables and then maximize the number of variables that are set to  $\bot$ .)

#### 5.1 Encoding Using Boolean Functions

To encode the machine  $M = (I, O, Q, q_{init}, \delta, \lambda)$  as AIG, we assume, without loss of generality, that each state is associated to a unique number in  $\{0, \dots |Q| - 1\}$  where the initial state  $q_{init}$  corresponds to 0.

We use a set of  $N = \lceil \log_2(|Q|) \rceil$  latches to remember the current state of the machine. For a latch  $\ell \in \{\ell_0, \ell_1, \dots, \ell_{N-1}\}$ , we write  $\nu_\ell$  its current Boolean value.

Our first step is to convert the IGMM into a set of Boolean functions that represents the behavior of the controller. That is, each output signal  $o \in O$  is associated to a Boolean function  $f^o$  that can be computed using the current value of the latches and the current value of each input signal. Similarly, for each  $\ell$ , there exists a function  $f^\ell$  that computes its next value based on the current values of all latches and input signals.

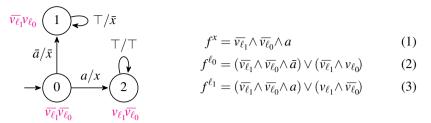

As an example, Figure 15 shows a possible encoding for the IGMM of Figure 5. (We do not use Fig. 6 because the Boolean encoding would be too simple to illustrate the upcoming variants of AIG encoding.)

Algorithm 3 shows how these functions are computed from the input IGMM. Initially, all output and latch functions are initialised to the false formula (lines 3–4). Then for each state q, lines 6–11 compute a Boolean formula  $f^q$  representing its encoding using latches. Here, the function  $\operatorname{BinaryEnc}(q)$  returns the array of  $\lceil \log_2(|Q|) \rceil$  Boolean values corresponding to the binary encoding of q. Then the loop on line 12 considers the edges leaving q for each input valuation u: if the output of that edge is not completely specified, an output valuation  $v \in \mathbb{B}^O$  is chosen with ChooseOneValuation on line 16. (For instance, in Figure 15 this function chooses to output  $\bar{x}$  for any input read from state 2.) For each latch  $\ell$  that should be true in the encoding of the destination state, lines 17–19 add the clause  $f^q \wedge u$  to  $f^\ell$ . And similarly, for each output signal o that is true in v, lines 20–22 add that clause to the formula  $f^o$ .

**Fig. 15**: Possible Boolean encoding of the IGMM of Figure 5. Two latches  $\ell_0$  and  $\ell_1$  are used to keep track of the current state of the machine. Function  $f^x$  specifies that x should be emitted only if we are in state 0 (encoded with  $\overline{\nu_{\ell_1}} \wedge \overline{\nu_{\ell_0}}$ ) and if a is read. It implies that  $\overline{x}$  will be output in other cases (therefore this encoding has made the choice to output  $\overline{x}$  from state 2). Functions  $f^{\ell_0}$  and  $f^{\ell_1}$  give similar conditions for the values of the latches.

#### Algorithm 3 ToSymbolicMealy

```

1: Input: IGMM M = (I, O, Q, q_{init}).

2: Output: Boolean functions for all outputs and latches.

3: \forall j \in \{0,\ldots,N-1\}: f^{\ell_j} \leftarrow \bot

4: \forall o \in O : f^o \leftarrow \bot

5: for q \in Q do

f^q = \top

6:

for j \in \{0, ..., N-1\} do

7:

\triangleright Encode q as a conjunction of latches

if BinaryEnc(q)[j] then

8:

f^q \leftarrow f^q \wedge v_{\ell_i}

9:

else

10:

f^q \leftarrow f^q \wedge \bar{v}_{\ell}

11:

for u \in \mathbb{B}^I do

▶ Update all functions for each input

12:

if \delta(q,u) is undefined then

13:

continue

14:

q' = \delta(q, u)

15:

v = \mathsf{ChooseOneValuation}(\lambda(q, u))

16:

for j \in \{0, ..., N-1\} do

17:

if BinaryEnc(q')[j] then

18:

f^{\ell_j} \leftarrow f^{\ell_j} \vee (f^q \wedge u)

19:

for o \in O do

20:

if v(o) = \top then

21:

\begin{array}{c} f^o \leftarrow f^o \lor (f^q \land u) \\ \textbf{return} \ \left\{ f^o \mid o \in O \right\}, \left\{ f^\ell \mid \ell \in \{\ell_0, \dots \ell_{N-1}\} \right\} \end{array}

22:

```

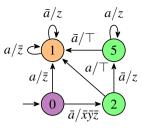

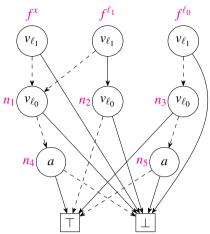

**Fig. 16**: BDD representation of  $f^x$ ,  $f^{\ell_0}$ , and  $f^{\ell_1}$  from Figure 15. A BDD is like a decision tree with sharing of identical subtrees. Each round node is labeled by a Boolean variable that is questioned, plain edges should be followed when the variable is true, and dashed edges when it is false. Variables always appear in the same order along a branch.

In our implementation, these Boolean functions are represented using *Binary Decision Diagrams* (BDD) (Bryant, 1986). Continuing the example of Figure 15, Figure 16 shows how  $f^{\ell_0}$ ,  $f^{\ell_1}$  and  $f^x$  are stored. These Boolean functions then have to be encoded into an AIG. The next two sections propose two different encodings.

# 5.2 If-Then-Else Encoding

Our first AIG encoding is inspired from the BDD representation of our functions. Assuming an order over the variables has been fixed, the BDD representation of a function can be seen as an If-The-Else normal form where each node v can be

read as "if v then  $n_1$  else  $n_2$ ".

This can be naturally encoded as  $(v \wedge n_1) \vee (\bar{v} \wedge n_2)$ , or, since we should be only using NOT and AND gates,  $\overline{v \wedge n_1} \wedge \overline{\bar{v} \wedge n_2}$ . That expression can of course be simplified when  $n_1$  and  $n_2$  are  $\top$  or  $\bot$ .

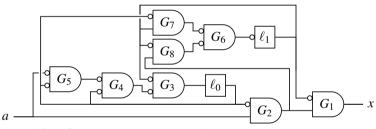

Continuing our running example, Figure 17 shows the AIG encoding for each node of Figure 16, and Figure 18 shows the circuit assembled from those parts.

This encoding uses at most three gates per node in the BDD representation of all Boolean functions. It is also sensitive to the ordering of variables in the BDD representation.

$$f^{x} = (v_{\ell_{1}} \wedge \bot) \vee (\overline{v_{\ell_{1}}} \wedge n_{1}) = \overline{v_{\ell_{1}}} \wedge n_{1}$$

$$n_{1} = (v_{\ell_{0}} \wedge \bot) \vee (\overline{v_{\ell_{0}}} \wedge n_{4}) = \overline{v_{\ell_{0}}} \wedge n_{4}$$

$$n_{4} = (a \wedge \top) \vee (\overline{a} \wedge \bot) = a$$

$$r_{4} = (v_{\ell_{1}} \wedge \bot) \vee (\overline{v_{\ell_{1}}} \wedge n_{3}) = \overline{v_{\ell_{1}}} \wedge n_{3}$$

$$n_{5} = (v_{\ell_{1}} \wedge \bot) \vee (\overline{v_{\ell_{0}}} \wedge n_{5}) = \overline{v_{\ell_{0}}} \wedge \overline{v_{\ell_{0}}} \wedge \overline{v_{\delta_{0}}} \wedge \overline{v_{\delta_{0}}}$$

$$n_{5} = (a \wedge \bot) \vee (\overline{a} \wedge \top) = \overline{a}$$

$$r_{6} = (v_{\ell_{1}} \wedge n_{2}) \vee (\overline{v_{\ell_{1}}} \wedge n_{1})$$

$$= \overline{(v_{\ell_{1}} \wedge n_{2})} \wedge \overline{(v_{\ell_{1}}} \wedge n_{1})$$

$$= \overline{(v_{\ell_{1}} \wedge n_{2})} \wedge \overline{(v_{\ell_{1}}} \wedge \overline{v_{1}})$$

$$n_{1} = \overline{(v_{\ell_{0}} \wedge \bot)} \vee \overline{(v_{\ell_{0}}} \wedge \overline{v_{\ell_{0}}} \wedge \overline{v_{\ell$$

**Fig. 17**: Step-by-step encoding of functions  $f^x$ ,  $f^{\ell_0}$ , and  $f^{\ell_1}$  as And-Inverter Graphs, based on the If-Then-Else normal form of these functions, naturally visible in Figure 16.

Fig. 18: Full circuit assembled from the bits in Figure 17.

# 5.3 Irredundant-Sum-Of-Products Encoding

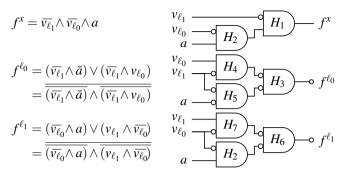

An alternative way to encode Boolean functions using AND and NOT gates, is to first rewrite these Boolean functions into disjunctive normal form (also known as sum-of-products). In particular there exist BDD-based algorithms to compute so called *irredundant sum-of-products* (ISOP) where each product is a prime implicant that cannot be removed without changing the function (Minato, 1992).

Figures 19–20 show this encoding of our running example.

However, note that (regardless of the encoding used) the encoder can easily detect that a gate computing a combination of signals already exists, and reuse it. This is the case of gate  $H_2$  in Figure 19.

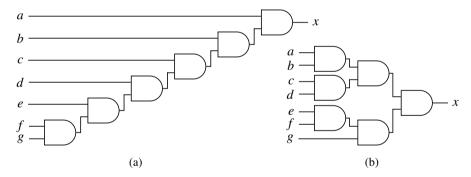

Without the above optimization, this encoding would use as many gates as symbols  $\vee$  or  $\wedge$  in the ISOP of the encoded function. Each product of the ISOP can be also encoded in multiple ways (Figure 21), and the same is true for the encoding of their sum.

**Fig. 19**: Encoding of functions  $f^x$ ,  $f^{\ell_0}$ ,  $f^{\ell_1}$  as And-Inverter Graphs based on Irredundant Sums-of-Products.

Fig. 20: Full circuit assembled from the bits of Figure 19.

**Fig. 21**: The product  $a \land b \land c \land d \land e \land f \land g$  requires 6 gates that can be arranged as a binary tree of any shape.

In SYNTCOMP, only the number of gates and latches is taken into consideration to measure the quality of the generated circuit. Another measure that could be used is the delay between the input and output: i.e., the number of gates on the longest path through the circuit. Balancing the binary tree of gates encoding *n*-ary conjunctions and disjunctions helps reducing this delay and improving the sharing of gates in the circuit (as will be discussed below).

#### 5.4 Other Improvements to the Encoding

#### **Dual Encoding**

An idea to reduce the number of gates needed is to check whether it is easier to encode the function itself or its negation. So instead of encoding  $f^x = a \lor b \lor c$  we can encode  $f^{\bar{x}} = \bar{a} \land \bar{b} \land \bar{c}$  and negate the output. This can, depending on the function, lead to substantial gains.

#### **Choosing the Specialization and Using Flexibility**

The IGMM used within ltlsynt is strictly more expressive than *traditional* Mealy machines, as they associate to a state and input valuation a set of outputs (the elements of which all satisfy the specification). However, the actual circuit cannot represent sets of outputs, but needs to respond to a concrete input valuation with a concrete output valuation. In Algorithm 3, the function ChooseOneValuation picks one of the compatible output valuations, which is then used to construct a circuit.

We use the following heuristic to choose a cube (over the output variables) such that

- All valuations compatible with the cube are compatible with the original condition.

- It minimizes the cost function  $\alpha.nhigh + \beta.nlow + \gamma.ndc$  with *nhigh* being the number of outputs set to  $\top$ , *nlow* being the number of outputs set to  $\bot$  and *ndc* being the number of outputs that do not appear in the cube.  $\alpha, \beta, \gamma$  are fixed nonnegative integer values corresponding to costs.

For instance, assume we have  $\delta(q,\ell) = xyz \vee x\bar{z}$  for some q and  $\ell$  with  $O = \{x,y,z\}$ . The compatible cubes are xyz and  $x\bar{z}$  with the respective costs  $3\alpha$  and  $\alpha + \gamma + \beta$ .

We typically use costs such that  $\beta < \gamma < \alpha$ . The reasoning behind this is simple: we prefer an output that is set to  $\bot$  as in such a case there is no need to encode the current transition hopefully leading to fewer gates. The opposite case with the output being set to  $\top$  is, usually, the least favorable as here the transition must be encoded. In between we have variables which do not appear (also referred to as *do-not-care* or just dc variables) in the cube, which can therefore be set to  $\top$  or  $\bot$ .

Finally, we can use this information about the do-not-care in the following way: for each output o we build two Boolean functions, one denoted  $f^o$  which corresponds to the cases where o *must* be set to  $\top$ . The second one, denoted  $f^{o,dc}$ , corresponds to cases where o *can* be set to  $\top$ . We can then proceed to encode  $f^o$  and  $f^o \lor f^{o,dc}$  and use whichever results in fewer gates.

#### **Increase Gate Sharing**

So far we have seen heuristics which try to minimize the number of gates needed to represent a given Boolean function. Another important aspect is to increase the number of gates which are shared between different Boolean functions. Indeed, the symbolic representation of the Mealy machine to be encoded has one function per

latch and output. Increasing the number of gates shared between these outputs might therefore yield significant overall reductions.

In the case of the ITE construction, this idea comes down to reordering the variables within the BDD. In order for this to be effective, the BDD variables would have to be reordered with respect to the Boolean functions to be encoded (and only those). Unfortunately we are currently not able to do this, due to the architecture of Spot.

However, we can use this idea and apply it to the ISOP construction. To this end we split the tree generated for each product (a cube) and arrange it into two subtrees: one connecting latches, and one connecting input variables. The intuition is that such a decoupling should increase the chance of reusing the gate to encode another function: particular valuations of the latches, or valuations of input variables are likely to be reused elsewhere in the circuit

#### **Other Implementation Details**

As shown in Figure 7 (and discussed later in Section 7.3) we seek to decompose the given formula if possible (Finkbeiner et al, 2021). In the case where decomposition is successful, multiple IGMMs have to be encoded jointly into a single AIG.

For the decomposition to be successful, the set of output variables of the different IGMMs built have to form a partition of all controllable propositions. The output of each IGMM can therefore be computed separately without any dependency between the different machines.

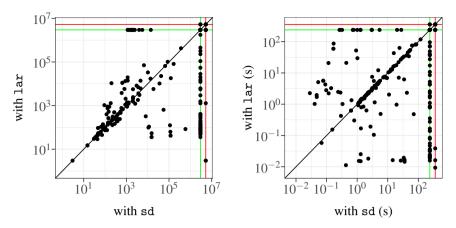

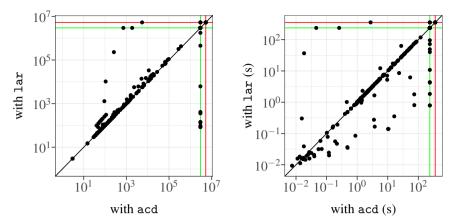

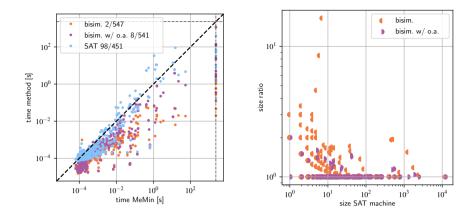

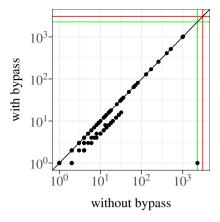

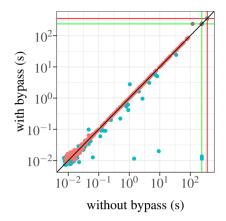

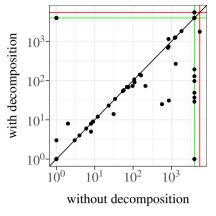

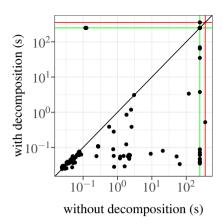

We can therefore take the following approach: each Mealy machine is associated to its own set of latches of appropriate size. Then Algorithm 3 is run for each of the machines and the resulting Boolean functions are encoded indifferently.