# Instruction scheduling

Akim Demaille, Etienne Renault, Roland Levillain

May 9, 2016

#### Table of contents

- Dependencies

- Dependency graph

- Instruction Pipeline

- Minimizing stalls

- 5 Loops unrolling

- Managing caches

### Dependencies analysis 1/2

Two instructions are independent they can be permuted without altering the consistency

# Dependencies analysis 1/2

Two instructions are independent they can be permuted without altering the consistency

The 3 following instructions are independent

$\begin{array}{lll} \mathsf{inst}_1: & \mathsf{a} \leftarrow \mathsf{42} \\ \mathsf{inst}_2: & \mathsf{b} \leftarrow \mathsf{51} \\ \mathsf{inst}_3: & \mathsf{c} \leftarrow \mathsf{0} \end{array}$

# Dependencies analysis 1/2

Two instructions are independent they can be permuted without altering the consistency

The 3 following instructions are independent

$$\begin{array}{ll} \mathsf{inst}_1: & \mathsf{a} \leftarrow \mathsf{42} \\ \mathsf{inst}_2: & \mathsf{b} \leftarrow \mathsf{51} \\ \mathsf{inst}_3: & \mathsf{c} \leftarrow \mathsf{0} \end{array}$$

• inst<sub>1</sub>, inst<sub>2</sub> and inst<sub>3</sub> can then be reordered

# Dependencies analysis 2/2

Two instructions are dependent if the first one needs to be executed before the second one.

### Dependencies analysis 2/2

Two instructions are dependent if the first one needs to be executed before the second one.

The 3 following instructions are dependent, i.e. no reordering is possible!

$\begin{array}{ll} \mathsf{inst}_1: & \mathsf{a} \leftarrow \mathsf{42} \\ \mathsf{inst}_2: & \mathsf{b} \leftarrow \mathsf{a} + \mathsf{51} \\ \mathsf{inst}_3: & \mathsf{c} \leftarrow \mathsf{b} \times \mathsf{12} \end{array}$

# Dependencies analysis 2/2

Two instructions are dependent if the first one needs to be executed before the second one.

The 3 following instructions are dependent, i.e. no reordering is possible!

$$\begin{array}{ll} \mathsf{inst}_1: & \mathsf{a} \leftarrow \mathsf{42} \\ \mathsf{inst}_2: & \mathsf{b} \leftarrow \mathsf{a} + \mathsf{51} \\ \mathsf{inst}_3: & \mathsf{c} \leftarrow \mathsf{b} \times \mathsf{12} \end{array}$$

- Two kind of dependencies:

- ▶ Data dependencies: the instruction manipulates a "variable" computed by another instruction.

- ▶ **Instruction dependencies**: the instruction is a "cjump", the next instruction depends of the "cjump".

### Read after Write (RAW)

An instruction reads from a location after an earlier instruction has written to it.

### Read after Write (RAW)

An instruction reads from a location after an earlier instruction has written to it.

$inst_1$ : lw \$2, 0(\$4)  $inst_2$ : addi \$6, \$2, 42

# Read after Write (RAW)

An instruction reads from a location after an earlier instruction has written to it.

$inst_1$ : lw \$2, 0(\$4)  $inst_2$ : addi \$6, \$2, 42

$inst_1$  and  $inst_2$  cannot be permuted, otherwise  $inst_2$  would read an old value for \$2

# Write after Read (WAR)

An instruction writes to a location after an earlier instruction has read from it.

# Write after Read (WAR)

An instruction writes to a location after an earlier instruction has read from it.

inst<sub>1</sub>: lw \$2, 0(\$4)

$inst_2$ : addi \$4, \$12, 42

# Write after Read (WAR)

An instruction writes to a location after an earlier instruction has read from it.

inst<sub>1</sub>: lw \$2, 0(\$4) inst<sub>2</sub>: addi \$4, \$12, 42

$inst_1$  and  $inst_2$  cannot be permuted, otherwise  $inst_1$  would read a new value for \$4

# Write after Write (WAW)

An instruction writes to a location after an earlier instruction has written to it.

# Write after Write (WAW)

An instruction writes to a location after an earlier instruction has written to it.

inst<sub>1</sub>: add \$1, \$2, \$3 inst<sub>2</sub>: add \$1, \$5, \$6

# Write after Write (WAW)

An instruction writes to a location after an earlier instruction has written to it.

inst<sub>1</sub>: add \$1, \$2, \$3 inst<sub>2</sub>: add \$1, \$5, \$6

$\mathsf{inst}_1$  and  $\mathsf{inst}_2$  cannot be permuted, otherwise  $\mathsf{inst}_1$  would write an old value in \$1

# Why and When reordering?

We would like to reorder the instructions within each basic block in a way which:

- preserves the dependencies between those instructions (and hence the correctness of the program)

- achieves the minimum possible number of pipeline stalls, i.e. two instructions simultaneously in the pipeline manipulates same data, registers, etc.

The two problems can be addressed separately (whew!).

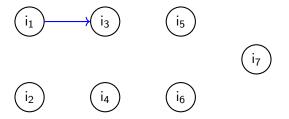

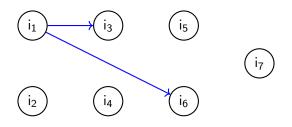

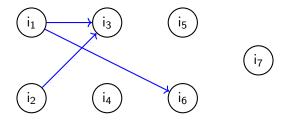

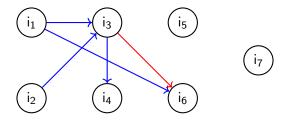

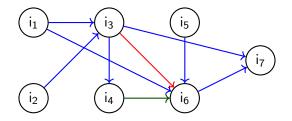

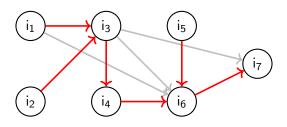

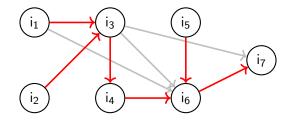

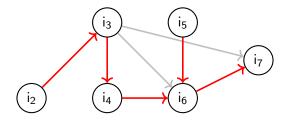

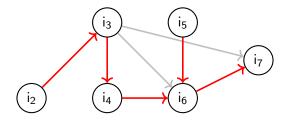

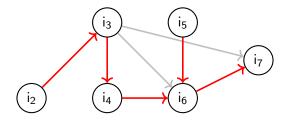

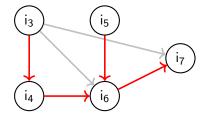

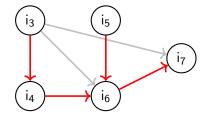

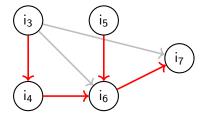

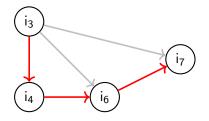

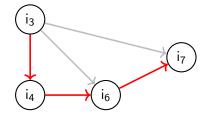

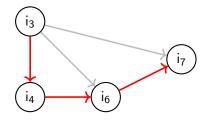

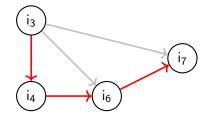

### Preserving and computing dependencies?

We construct a directed acyclic graph (DAG) to represent the dependencies between instructions:

- For each instruction in the basic block, create a corresponding vertex in the graph

- For each dependency between two instructions, create a corresponding (annotated) edge in the graph. Note that this edge is annotated.

$$i_2$$

$i_4$

$(i_1)$

$\left(i_{3}\right)$

$\left(i_{5}\right)$

$(i_2)$

$\left(i_{4}\right)$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_6: add $3,$1,$2 | i_6: add $3,$1,$4

```

$$(i_2)$$

$(i_1)$

$(i_3)$

$\left(i_{5}\right)$

$(i_2)$

$\left(i_{4}\right)$

$(i_6)$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_6: add $3,$1,$2

```

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_6: add $3,$1,$2

```

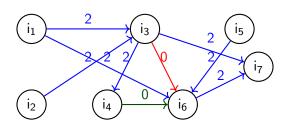

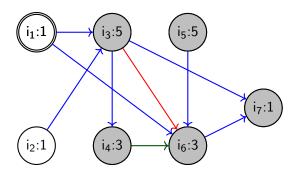

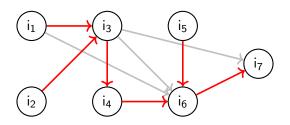

# Preserving dependencies: Critical Path 1/2

The critical path represents the longest path between two nodes. We add delays (weights) to edges:

- 0 for WAW and WAR dependencies

- 2 for RAW dependencies with memory access

- 1 for other RAW dependencies

# Preserving dependencies: Critical Path 1/2

The critical path represents the longest path between two nodes. We add delays (weights) to edges:

- 0 for WAW and WAR dependencies

- 2 for RAW dependencies with memory access

- 1 for other RAW dependencies

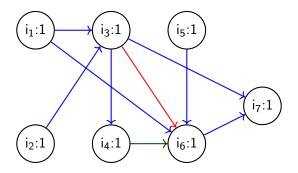

# Preserving dependencies: Critical Path 2/2

Any (reverse) topological sort of this DAG (i.e. any linear ordering of the vertices which keeps all the edges pointing forwards) will maintain the dependencies and hence preserve the correctness of the program.

#### Algorithm:

- Associate a weight 1 to all "instruction node"

- For all nodes ni in topological postorder

- ▶ If n; is not a leaf

- \* For all nodes  $n_j$  in  $succ(n_i)$  do  $n_i.weight \leftarrow max(n_i.weight, n_j.weight+ delay(n_i, n_j))$

Remember "important" edges during computations, they will form the critical path.

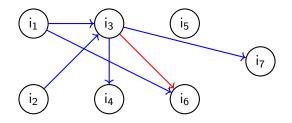

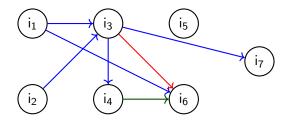

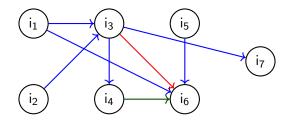

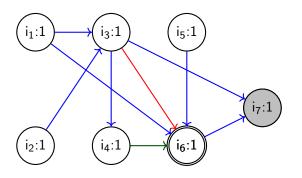

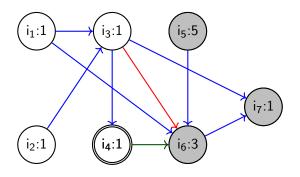

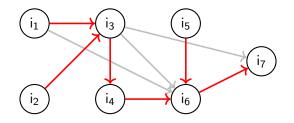

Delays: blue arrows 2, red and green 0

Delays: blue arrows 2, red and green 0

i<sub>7</sub> doesn't have successors, skip it!

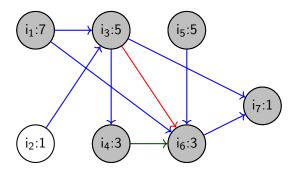

Delays: blue arrows 2, red and green 0

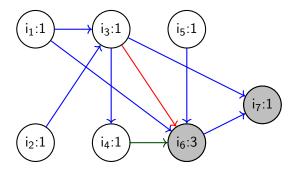

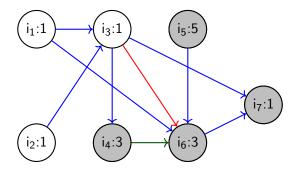

$delay(i_6, i_7)=2 > 1$ , change  $i_6$  weight!

Delays: blue arrows 2, red and green 0

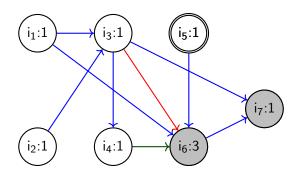

Delays: blue arrows 2, red and green 0

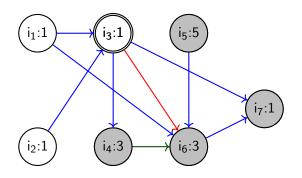

$delay(i_5, i_6)=2 > 1$ , change  $i_5$  weight!

Delays: blue arrows 2, red and green 0

Delays: blue arrows 2, red and green 0

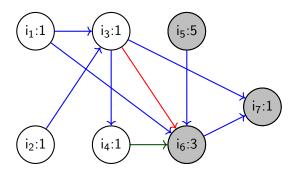

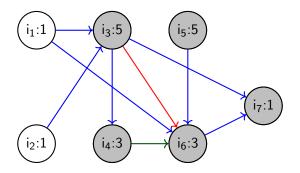

$i_6.weight=3 > 1$ , change  $i_4$  weight!

Delays: blue arrows 2, red and green 0

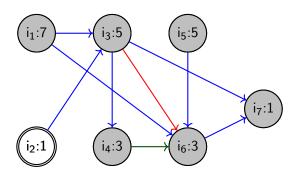

Delays: blue arrows 2, red and green 0

$delay(i_3, i_4) + i_4.weight=3 > 1$ , change  $i_3$  weight!

Delays: blue arrows 2, red and green 0

Delays: blue arrows 2, red and green 0

$delay(i_1, i_3) + i_3.weight=7 > 1$ , change  $i_1$  weight!

Delays: blue arrows 2, red and green 0

Delays: blue arrows 2, red and green 0

$delay(i_2, i_3) + i_3.weight=7 > 1$ , change  $i_2$  weight!

Delays: blue arrows 2, red and green 0

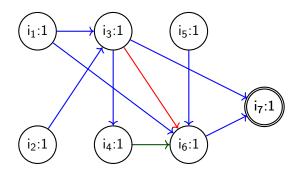

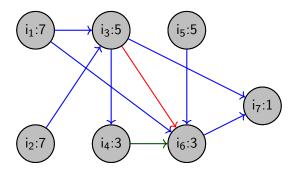

## So many orders . . . with one critial path

$i_1, i_2, i_3, i_4, i_5, i_6, i_7$  $i_1, i_2, i_5, i_3, i_4, i_6, i_7$  i<sub>1</sub>,i<sub>2</sub>,i<sub>3</sub>,i<sub>5</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>2</sub>,i<sub>1</sub>,i<sub>5</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>5</sub>,i<sub>1</sub>,i<sub>2</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub>  $i_2, i_1, i_3, i_5, i_4, i_6, i_7$   $i_1, i_5, i_2, i_3, i_4, i_6, i_7$  $i_5, i_2, i_1, i_3, i_4, i_6, i_7$

i<sub>2</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>5</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>2</sub>,i<sub>5</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub>

### So many orders ... with one critial path

$i_1, i_2, i_3, i_4, i_5, i_6, i_7$  $i_1, i_2, i_5, i_3, i_4, i_6, i_7$  i<sub>1</sub>,i<sub>2</sub>,i<sub>3</sub>,i<sub>5</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>2</sub>,i<sub>1</sub>,i<sub>5</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>5</sub>,i<sub>1</sub>,i<sub>2</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>2</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>5</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>1</sub>,i<sub>5</sub>,i<sub>2</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>5</sub>,i<sub>2</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub>

i<sub>2</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>5</sub>,i<sub>6</sub>,i<sub>7</sub> i<sub>2</sub>,i<sub>5</sub>,i<sub>1</sub>,i<sub>3</sub>,i<sub>4</sub>,i<sub>6</sub>,i<sub>7</sub>

All these permutations respect dependencies but is there a best instruction scheduling?

## Performances and Pipeline

#### Not all orders are equivalents!

- Some dependencies can bring hazards that slow down performances inside of the pipeline

- Hazard occurs when:

- ▶ 1 instruction requires the previous instruction has finished

- ▶ 2 instructions need the same data at the same time: one of the two is blocked

## Instructions Pipeline

The microprocessor (MIPS) contains 5 stages:

- IF: Instruction Fetch

- ID: Instruction Decode. Read operands from registers, compute the address of the next instruction

- EX Execute instructions requiring the ALU

- ME Read/write into Memory

- WB Write Back. Results are written into registers.

|                    | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> | cycle <sub>8</sub> | cycle <sub>9</sub> |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| instr <sub>1</sub> | IF                 | ID                 | EX                 | ME                 | WB                 |                    |                    |                    | i                  |

| instr <sub>2</sub> |                    | IF                 | ID                 | EX                 | ME                 | WB                 |                    |                    |                    |

| instr <sub>3</sub> |                    | I                  | IF                 | ID                 | EX                 | ME                 | WB                 |                    | ;                  |

| instr <sub>4</sub> | <br>               | !<br>              |                    | IF                 | ID                 | EX                 | ME                 | WB                 | 1                  |

| instr <sub>5</sub> | 1                  | l<br>ı             | l                  |                    | IF                 | ID                 | EX                 | ME                 | WB                 |

# Hazard: RAW dependencies 1/2

Some instruction requires a result computed by a previous one!

#### Consider the following example:

|                   | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> |

|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| lw \$2, 0(\$4)    | IF                 | ID                 | EX                 | ME                 | WB                 | '                  |                    |

| addi \$5, \$2, 10 |                    | IF                 | ID                 |                    | EX                 | ME                 | WB                 |

- 1w produces its result into \$2 during the ME stage

- ADDI requires \$2 for the EX stage

- In this example, 1 stall (cycle 4)

The goal of risc architectures is to produce one per cycle!

# Hazard: RAW dependencies 2/2

#### Consider now the following example:

|                     | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> | cycle <sub>8</sub> |   |

|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---|

| lw \$2, 0(\$4)      | IF                 | ID                 | EX                 | ME                 | WB                 |                    |                    | ı                  | ı |

| addi \$5, \$2, 10   |                    | IF                 | ID                 |                    | ¥ΕΧ                | ME                 | WB                 |                    | 1 |

| add \$12, \$9, \$11 |                    |                    | IF                 |                    | ID                 | EX                 | $^{ m ME}$         | WB                 |   |

# Hazard: RAW dependencies 2/2

#### Consider now the following example:

|                     | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> | cycle <sub>8</sub> |

|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| lw \$2, 0(\$4)      | IF                 | ID                 | EX                 | ME                 | WB                 |                    |                    |                    |

| addi \$5, \$2, 10   |                    | IF                 | ID                 |                    | ¥ΕΧ                | ME                 | WB                 |                    |

| add \$12, \$9, \$11 |                    |                    | IF                 |                    | ID                 | EX                 | ME                 | WB                 |

Let's look ...instruction 3 is independent from the others

# Hazard: RAW dependencies 2/2

#### Consider now the following example:

|                     | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> | cycle <sub>8</sub> |

|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| lw \$2, 0(\$4)      | IF                 | ID                 | EX                 | ME                 | WB                 |                    |                    | ı                  |

| addi \$5, \$2, 10   |                    | IF                 | ID                 |                    | ¥ΕΧ                | ME                 | WB                 | I                  |

| add \$12, \$9, \$11 |                    |                    | IF                 |                    | ID                 | EX                 | ME                 | WB                 |

# Let's look ... instruction 3 is independent from the others so we can change the order!

|                     | $cycle_1$ | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> | cycle <sub>7</sub> | cycle <sub>8</sub> |   |

|---------------------|-----------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---|

| lw \$2, 0(\$4)      | IF        | ID                 | EX                 | ME                 | WB                 |                    | i                  | '<br>              | ı |

| add \$12, \$9, \$11 |           | IF                 | ID                 | EX                 | ME                 | WB                 |                    | <br>               | 1 |

| addi \$5, \$2, 10   |           |                    | IF                 | ID                 | <b>≯</b> EX        | ME                 | WB                 |                    | 1 |

## Hazard: WAW dependencies

#### Two instructions write in the same register!

#### Consider the following example:

|                    | cycle <sub>1</sub> | cycle <sub>2</sub> | cycle <sub>3</sub> | cycle <sub>4</sub> | cycle <sub>5</sub> | cycle <sub>6</sub> |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| addi \$5, \$11, 42 | IF                 | ID                 | EX                 | ME                 | WB                 | ] '                |

| addi \$5, \$2, 10  |                    | IF                 | ID                 | EX                 | ME                 | ₩B                 |

WAW do not produce stalls! (even when writing in the same memory address)

## Hazard: WAR dependencies

#### One instruction writes where a previous one reads!

#### Consider the following example:

WAR do not produce stalls!

## Back to the example - without scheduling

|                | c <sub>1</sub> | c <sub>2</sub> | с3 | C4  | C5         | С6 | C7         | С8 | Cg . | c <sub>10</sub> | c <sub>11</sub> | c <sub>12</sub> | c <sub>13</sub> |

|----------------|----------------|----------------|----|-----|------------|----|------------|----|------|-----------------|-----------------|-----------------|-----------------|

| $i_1$          | IF             | ID             | EX | ME  | WB         |    |            |    |      | '<br>           | ·               |                 |                 |

| i <sub>2</sub> |                | IF             | ID | EX  | $^{ m ME}$ | WB |            |    |      | l j             | ı i             |                 | 1               |

| i <sub>3</sub> |                | ı              | IF | ID  |            | EX | $^{ m ME}$ | WB |      | l<br>1          |                 |                 | ı               |

| i <sub>4</sub> |                | l              | ı  | IF  |            | ID | EX         | ME | WB   |                 |                 |                 | <u> </u>        |

| i <sub>5</sub> |                | '<br>          | I  | ı   |            | IF | ID         | EX | ME   | WB              |                 |                 | <u> </u>        |

| i <sub>6</sub> |                | I              | 1  | l I | 1          |    | IF         | ID |      | EX              | ME              | WB              |                 |

| i <sub>7</sub> |                | l              | l  |     | <br> -     |    | 1          | IF |      | ID              | EX              | ME              | WB              |

## Back to the example - without scheduling

|                | c <sub>1</sub> | c <sub>2</sub> | С3 | C4  | C5               | С6 | c <sub>7</sub> | C8     | Cg     | c <sub>10</sub> | c <sub>11</sub> | c <sub>12</sub> | c <sub>13</sub> |

|----------------|----------------|----------------|----|-----|------------------|----|----------------|--------|--------|-----------------|-----------------|-----------------|-----------------|

| $i_1$          | IF             | ID             | EX | ME  | $_{\mathrm{WB}}$ |    | !<br>!         | !<br>! |        | '<br>           | ·               |                 |                 |

| $i_2$          | ı              | IF             | ID | EX  | $_{ m ME}$       | WB |                | 1      | '<br>! | l į             | ı i             |                 | 1               |

| $i_3$          |                | I              | IF | ID  |                  | EX | ME             | WB     |        | l               |                 |                 | ı               |

| i <sub>4</sub> | <br>           | l              | ı  | IF  |                  | ID | EX             | ME     | WB     |                 |                 |                 | ! ;             |

| i <sub>5</sub> | I              | !<br>          | I  |     |                  | IF | ID             | EX     | ME     | WB              | !               |                 | <u>.</u>        |

| i <sub>6</sub> | I              | I              | I  | l i |                  |    | IF             | ID     |        | EX              | ME              | WB              | 1               |

| i <sub>7</sub> | l              | l              |    |     |                  |    | 1              | IF     |        | ID              | EX              | ME              | WB              |

|                |                |                |    |     |                  |    |                |        |        |                 |                 |                 |                 |

Without scheduling: 2 dependencies, 2 stalls, 13 cycles!

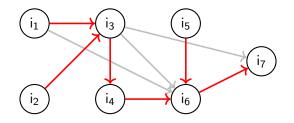

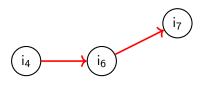

## Minimizing Stalls – First approach

Each time we emit the next instruction, we should try to choose one which

- P<sub>1</sub> does not conflict with the previous emitted instruction

- P2: is most likely to conflict if first of a pair (e.g. prefer lw to add)

- P<sub>3</sub>: is as far away as possible (along paths in the DAG) from an instruction which can validly be scheduled last

## Minimizing Stalls – First approach

Each time we emit the next instruction, we should try to choose one which

- P<sub>1</sub> does not conflict with the previous emitted instruction

- P2: is most likely to conflict if first of a pair (e.g. prefer lw to add)

- P<sub>3</sub>: is as far away as possible (along paths in the DAG) from an instruction which can validly be scheduled last

#### Algorithm:

- Compute the dependency graph

- While the list of candidate instructions is not empty

- If one instruction satisfies P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub>: remove it from the list and emit it.

- \* Remove the instruction from the DAG and insert the newly minimal elements into the candidate list.

- Otherwise emit a nop instruction

Candidates =  $\{i_1, i_2, i_5\}$ Final Order =

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_6: add $3,$1,$2

```

Candidates =

$$\{i_1, i_2, i_5\}$$

Final Order =

#### Choose $i_1$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_3: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_1, i_2, i_5\}

Final Order = i_1

```

#### Choose $i_1$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

Candidates = \{i_1, i_2, i_5\}

Final Order = i_1

```

#### Choose $i_1$ since it satisfies $P_1$ , $P_2$ and $P_3$

Candidates =  $\{i_2, i_5\}$ Final Order =  $i_1$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_2, i_5\}

Final Order = i_1

```

Choose  $i_2$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_2, i_5\}

Final Order = i_1, i_2

```

#### Choose $i_2$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

Candidates = \{i_2, i_5\}

Final Order = i_1, i_2

```

#### Choose $i_2$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

Candidates = \{i_5, i_3\}

Final Order = i_1, i_2

```

```

Candidates = \{i_5, i_3\}

Final Order = i_1, i_2

```

#### Choose $i_5$ since it satisfies $P_1$ , $P_2$ and $P_3$

4 D > 4 A > 4 B > 4 B > B 90 Q

```

Candidates = \{i_5, i_3\}

Final Order = i_1, i_2, i_5

```

#### Choose $i_5$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

Candidates = \{i_5, i_3\}

Final Order = i_1, i_2, i_5

```

#### Choose $i_5$ since it satisfies $P_1$ , $P_2$ and $P_3$

4 D > 4 D > 4 E > 4 E > E 9 9 9 9

```

Candidates = \{i_3\}

Final Order = i_1, i_2, i_5

```

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_3\}

Final Order = i_1, i_2, i_5

```

#### Choose $i_3$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_3\}

Final Order = i_1, i_2, i_5, i_3

```

#### Choose $i_3$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_3\}

Final Order = i_1, i_2, i_5, i_3

```

#### Choose $i_3$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_4\}

Final Order = i_1, i_2, i_5, i_3

```

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_4\}

Final Order = i_1, i_2, i_5, i_3

```

Choose  $i_4$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

4014914714717 7 000

```

i_1: lw $1,0($10) |i_4: sw $3,12($10) |i_7: sw $3,16($10) |i_2: lw $2,4($10) |i_5: lw $4,8($10) |i_6: add $3,$1,$2

```

```

Candidates = \{i_4\}

Final Order = i_1, i_2, i_5, i_3, i_4

```

#### Choose $i_4$ since it satisfies $P_1$ , $P_2$ and $P_3$

40 1 40 1 4 5 1 5 1 0 0

```

Candidates = \{i_4\}

Final Order = i_1, i_2, i_5, i_3, i_4

```

Choose  $i_4$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

40 40 40 40 40 000

```

Candidates = \{i_6\}

Final Order = i_1, i_2, i_5, i_3, i_4

```

```

Candidates = \{i_6\}

Final Order = i_1, i_2, i_5, i_3, i_4

```

Choose  $i_6$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

```

Candidates = \{i_6\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6

```

Choose  $i_6$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

$(i_7)$

```

Candidates = \{i_6\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6

```

Choose  $i_6$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

$(i_7)$

```

Candidates = \{i_7\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6

```

$(i_7)$

```

Candidates = \{i_7\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6

```

Choose  $i_7$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

```

Candidates = \{i_7\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6, i_7

```

#### Choose $i_7$ since it satisfies $P_1$ , $P_2$ and $P_3$

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10) | i_2: lw $2,4($10) | i_5: lw $4,8($10) | i_5: add $3,$1,$2 | i_6: add $3,$1,$4

```

```

Candidates = \{i_7\}

Final Order = i_1, i_2, i_5, i_3, i_4, i_6, i_7

```

Choose  $i_7$  since it satisfies  $P_1$ ,  $P_2$  and  $P_3$

Final Order =  $i_1$ ,  $i_2$ ,  $i_5$ ,  $i_3$ ,  $i_4$ ,  $i_6$ ,  $i_7$

|                | $c_1$ | c <sub>2</sub> | c <sub>3</sub> | c <sub>4</sub> | c <sub>5</sub> | c <sub>6</sub> | c <sub>7</sub> | c <sub>8</sub> | c <sub>9</sub> | c <sub>10</sub> | c <sub>11</sub> |  |

|----------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|--|

| $i_1$          | IF    | ID             | EX             | ME             | WB             |                |                |                | l<br>I         |                 | ' '<br>         |  |

| $i_2$          |       | IF             | ID             | EX             | ME             | WB             |                |                | I              | i               | 1               |  |

| i <sub>5</sub> | ļ i   |                | IF             | ID             | EX             | ME             | WB             |                | 1              | l l             |                 |  |

| $i_3$          |       |                | l              | IF             | ID             | EX             | ME             | WB             |                |                 | '               |  |

| i <sub>4</sub> |       |                | l              | 1              | IF             | ID             | EX             | ME             | WB             |                 | <u>'</u> 1      |  |

| i <sub>6</sub> | ۱ ۱   |                | l              | ı              | ı              | IF             | ID             | EX             | ME             | WB              |                 |  |

| i <sub>7</sub> |       |                | <br> -         |                |                |                | IF             | ID             | EX             | ME              | WB              |  |

```

i_1: lw $1,0($10) | i_4: sw $3,12($10) | i_7: sw $3,16($10)

i_2: lw $2,4($10) | i_5: lw $4,8($10)

i_3: add $3,$1,$2 | i_6: add $3,$1,$4

```

Final Order =  $i_1$ ,  $i_2$ ,  $i_5$ ,  $i_3$ ,  $i_4$ ,  $i_6$ ,  $i_7$

|                | $c_1$  | c <sub>2</sub> | c <sub>3</sub> | c <sub>4</sub> | c <sub>5</sub> | c <sub>6</sub> | c <sub>7</sub> | c <sub>8</sub> | c <sub>9</sub> | c <sub>10</sub> | c <sub>11</sub> |

|----------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|

| $i_1$          | IF     | ID             | EX             | ME             | WB             |                |                |                | !<br>          |                 | , ,             |

| $i_2$          |        | IF             | ID             | EX             | ME             | WB             |                |                | I              |                 | 1               |

| i <sub>5</sub> | l      |                | IF             | ID             | EX             | ME             | WB             |                | 1              |                 | ·               |

| $i_3$          | l<br>I |                |                | IF             | ID             | EX             | ME             | WB             |                |                 | 1               |

| i <sub>4</sub> |        |                | İ              |                | IF             | ID             | EX             | ME             | WB             |                 |                 |

| i <sub>6</sub> | l      |                | l              | ı i            |                | IF             | ID             | EX             | ME             | WB              | !               |

| $i_7$          |        |                |                |                |                |                | IF             | ID             | EX             | ME              | WB              |

With scheduling: still 2 dependencies but 0 stalls and 11 cycles!

# A word on scheduling strategies

- Sometimes we cannot avoid some stalls

- Computing the critical path can be smarter:

- ▶ Rather than attributing 1 as weight to every instruction, we can adjust according to the real time of executing the instruction

- We can take advantages of the number of successors

- ... many yet-to-be-define heuristics!

- Computing the DAG of dependencies can be done in  $O(n^2)$  by scanning backwards through the basic block and adding edges as dependencies arise

### A word on performances

We can statically compute instructions per cycle IPC= $\frac{\text{nb instructions}}{\text{nb cycles}}$ , to evaluate 2 possible scheduling.

In the previous example:

- without scheduling IPC= $\frac{7}{13}$  = 0.53

- with scheduling IPC= $\frac{7}{11}$  = 0.63 (better!)

We can also statically compute cycle per instructions:  $CPI = \frac{1}{IPC}$ .

The CPI lower bound is  $\frac{\sum \alpha \times \beta}{\text{nb instructions}}$ , avec  $\alpha$  is the number of instructions for a given instruction type and  $\beta$  the associated cost.

#### Can we do better?

#### Consider the following code (representing a basic block):

```

i_1: Loop: lw $t0, 0($s1) # t0=array element

i_2: addu $t0, $t0, $s2 # add scalar in s2

i_3: sw $t0, 0($s1) # store result

i_4: addi $s1, $s1,-4 # decrement pointer

i_5: bne $s1, $0, Loop # branch s1!=0

```

#### Can we do better?

#### Consider the following code (representing a basic block):

|                | c <sub>1</sub> | C2 | С3 | C4 | C5 | c6 | C7 | C8 | C9 | C10 | C11 | C <sub>12</sub> | C13 | C14 | C <sub>15</sub> | C16 |   |

|----------------|----------------|----|----|----|----|----|----|----|----|-----|-----|-----------------|-----|-----|-----------------|-----|---|

| i <sub>1</sub> | IF             | ID | EX | ME | WB |    |    |    | '  |     | 1   |                 |     |     |                 |     |   |

| i <sub>2</sub> |                | IF | ID |    | EX | ME | WB |    |    |     |     |                 |     |     |                 |     | ı |

| iз             | l              |    | IF |    |    |    |    | ID | EX | ME  | WB  |                 |     |     |                 |     | ı |

| i4             | l              | I  | Ī  |    |    |    |    | IF | ID | EX  | ME  | WB              |     |     |                 |     |   |

| i <sub>5</sub> |                |    |    |    |    |    | 1  |    | IF |     |     |                 | ID  | EX  | ME              | WB  |   |

|                |                |    |    |    |    |    |    |    |    |     |     |                 |     |     |                 |     |   |

#### Can we do better?

#### Consider the following code (representing a basic block):

| c <sub>1</sub> | c <sub>2</sub> | С3    | C4             | C5          | c <sub>6</sub> | C7                         | C8                             | C9                            | C10 | c <sub>11</sub>                                                                                                                                                                                                                                                                                                           | C <sub>12</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | c <sub>13</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C <sub>14</sub> | C <sub>15</sub> | c <sub>16</sub>       |

|----------------|----------------|-------|----------------|-------------|----------------|----------------------------|--------------------------------|-------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------|

| IF             | ID             | EX    | ME             | WB          |                |                            |                                |                               | '   | 1                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '               |                 |                       |

|                | IF             | ID    |                | EX          | ME             | WB                         | ] ,                            |                               |     |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l               |                 |                       |

|                |                | IF    |                |             |                |                            | ID                             | EX                            | ME  | WB                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ı               |                 | 1 1                   |

|                | I              |       |                |             |                |                            | IF                             | ID                            | EX  | ME                                                                                                                                                                                                                                                                                                                        | WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                 |                       |

| ·<br>I         |                |       | ı              |             |                |                            |                                | IF                            |     |                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EX              | ME              | WB                    |

|                | C <sub>1</sub> | IF ID | IF ID EX IF ID | IF ID EX ME | IF ID EX ME WB | IF ID EX ME WB IF ID EX ME | IF ID EX ME WB  IF ID EX ME WB | IF   ID   EX   ME   WB     WB | IF  | IF   ID   EX   ME   WB     WB     IF   ID   EX   ME   WB     ID   EX   ME   IF   ID   ID   ID   ID   ID   ID   ID | IF   ID   EX   ME   WB     IT   ID   EX   ME     ID   EX   ME     ID   EX   ME   ID   EX   ME     ID   EX   ME     ID   EX   ME     ID   EX   ME   ID   EX   ME     ID   EX   ME     ID   EX   ME     ID   EX   ME     ID   EX   ME     ID   EX   ME     ID   EX   EX   ID   EX   EX   ID   EX   EX   EX   EX   EX   EX   EX   E | IF   ID   EX   ME   WB     WB     IF   ID   EX   ME   WB     IF   ID   EX   EX   EX   EX   EX   EX   EX   E | F               | F               | F   ID   EX   ME   WB |

16 cycles for 5 instructions that are all dependent!

$$IPC = 0.31$$

## Loop Unrolling

- Replicate loop body to expose more parallelism

- Reduces loop-control overhead

## Loop Unrolling

- Replicate loop body to expose more parallelism

- Reduces loop-control overhead

At high level, it can be seen as following:

| Without Loop Unrolling                              | With Loop Unrolling                                  |

|-----------------------------------------------------|------------------------------------------------------|

| int i;                                              | int i;                                               |

| for $(i = 0; i < 100; ++i)$                         | for $(i = 0; i < 100; i+=5)$                         |

| for $(i = 0; i < 100; ++i)$<br>tab[i] = tab[i] +42; | for $(i = 0; i < 100; i+=5)$<br>tab[i] = tab[i] +42; |

|                                                     | tab[i+1] = tab[i+1] + 42;                            |

|                                                     | tab[i+2] = tab[i+2] + 42;                            |

|                                                     | tab[i+3] = tab[i+3] + 42;                            |

|                                                     | tab[i+4] = tab[i+4] + 42;                            |

## Loop Unrolling

- Replicate loop body to expose more parallelism

- Reduces loop-control overhead

At high level, it can be seen as following:

| Without Loop Unrolling      | With Loop Unrolling                                  |

|-----------------------------|------------------------------------------------------|

| int i;                      | int i;                                               |

| for $(i = 0; i < 100; ++i)$ | for $(i = 0; i < 100; i+=5)$                         |

| tab[i] = tab[i] +42;        | for $(i = 0; i < 100; i+=5)$<br>tab[i] = tab[i] +42; |

|                             | tab[i+1] = tab[i+1] + 42;                            |

|                             | tab[i+2] = tab[i+2] + 42;                            |

|                             | tab[i+3] = tab[i+3] + 42;                            |

|                             | tab[i+4] = tab[i+4] + 42;                            |

Special care must be taken for pre and post loops operations (as well as intra-loop dependencies)

34 / 57

```

٦w

$t0, 0($s1)

# t0=array element

Loop:

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1)

# store result

SW

i<sub>4</sub>:

addi

$s1, $s1,-4 # decrement pointer

$s1, $0, Loop # branch s1!=0

bne

lw

$t0, 0($s1)

# t0=array element

Loop:

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1)

# store result

SW

addi

$s1, $s1,-4

# decrement pointer

$s1, $0, Loop # branch s1!=0

bne

$t0, 0($s1) # t0=array element

Loop:

lw

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1) # store result

SW

$s1, $s1,-4

i<sub>14</sub>:

addi

# decrement pointer

$s1, $0, Loop

# branch s1!=0

bne

```

#### First duplicate N times the body of the loop!

```

Loop:

lw

$t0, 0($s1) # t0=array element

$t0, $t0, $s2 # add scalar in s2

addu

SW

$t0, 0($s1) # store result

addi

$s1, $s1,-4 # decrement pointer

$t0, 0($s1)

# t0=array element

٦w

$t0, $t0, $s2 # add scalar in s2

addıı

$t0, 0($s1)

# store result

SW

$s1, $s1,-4

# decrement pointer

addi

lw

$t0, 0($s1) # t0=array element

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1) # store result

SW

i<sub>14</sub>:

$s1, $s1,-4 # decrement pointer

addi

$s1, $0, Loop # branch s1!=0

bne

```

Remove redundant labels and jump (by supposing that we are able to do it!)

```

Loop:

lw

$t0, 0($s1) # t0=array element

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1) # store result

SW

i<sub>4</sub>:

addi

$s1, $s1,-4 # decrement pointer

$t1, 0($s1) # t0=array element

lw

addu

$t1, $t1, $s2 # add scalar in s2

$t1, 0($s1)

# store result

SW

addi

$s1, $s1,-4 # decrement pointer

٦w

$t2, 0($s1) # t0=array element

$t2, $t2, $s2 # add scalar in s2

addu

SW

$t2, 0($s1) # store result

i<sub>14</sub>:

addi

$s1, $s1,-4 # decrement pointer

$s1, $0, Loop # branch s1!=0

bne

```

Use other temporaries name when possible!

```

$s1, $s1,-12 # decrement pointer

i4:

Loop:

addi

$t0, 0($s1) # t0=array element

lw

$t0, $t0, $s2 # add scalar in s2

addu

$t0, 0($s1) # store result

SW

٦w

$t1, 4($s1) # t0=array element

$t1, $t1, $s2 # add scalar in s2

addıı

$t1, 4($s1) # store result

SW

$t2, 8($s1) # t0=array element

lw

addıı

$t2, $t2, $s2 # add scalar in s2

t2, t2, t3 t4 store result

SW

$s1, $0, Loop # branch s1!=0

bne

```

Grab redundant operation and merge them carefully!

```

\$s1, \$s1, -12 # decrement pointer for N=3

Loop:

addi

$t0, 0($s1)

# t0=array element

lw

lw

$t1, 4($s1) # t1=array element

lw

$t2, 8($s1) # t2=array element

$t0, $t0, $s2 # add scalar in s2

addu

$t1, $t1, $s2 # add scalar in s2

addu

$t2, $t2, $s2 # add scalar in s2

addu

$t0, 0($s1)

# store result

SW

$t1, 4($s1) # store result

SW

$t2, 8($s1) # store result

SW

$s1, $0, Loop # branch s1!=0

bne

```

Schedule the instructions and renumber them (and update comments)!

#### Pros & Cons

- We avoid a lot of conditional jumps (and many stall hence)

- We require 19 cycles for 11 instructions: IPC=0.57 (a lot better than the previous 0.31)

- This trick allows to have more independent instructions to insert, and thus, less stalls!

- But we have now a prologue and an epilogue: i.e., two more basic blocks

- Require more temporaries: register allocation will be harder!

- Try it by yourself in gcc -funroll-loops

#### A very last word on Branch Hazards 1/2

- Conditional jumps often introduce delays since we cannot pre-fetch instrcutions

- ► Branch Outcome and Branch Target Address are ready at the end of the EX stage (3th stage)

- Conditional branches are solved when PC is updated at the end of the ME stage (4th stage)

- Can we avoid them?

#### We only know $i_{next}$ at cycle 5!

|                   | $c_1$  | $c_2$  | c3 | C4 | c <sub>5</sub> | c <sub>6</sub> | c <sub>7</sub> | C8      | Cg |

|-------------------|--------|--------|----|----|----------------|----------------|----------------|---------|----|

| bne \$1,\$2, loop | IF     | ID     | EX | ME | WB             |                | · '            | ' '<br> | 1  |

| nop               | l<br>I | IF     | ID | EX | ME             | WB             |                |         | 1  |

| nop               | ı      | ı      | IF | ID | EX             | $^{ m ME}$     | WB             |         | i  |

| nop               | l<br>I | '<br>  |    | IF | ID             | EX             | $^{ m ME}$     | WB      | 1  |

| i <sub>next</sub> | 1      | l<br>I |    |    | IF             | ID             | EX             | ME      | WB |

#### A very last word on Branch Hazards 2/2

- X delayed slot: the X instructions after a branch are systematically executed

- The original SPARC and MIPS processors each used a single branch delay slot to eliminate single-cycle stalls after branches

- We need branch prediction... but nowadays, most of processors do it for us (and use slt...)!

- Some architectures have bypass between stages to avoid stalls

Avoid as possible floating points and jumps!

#### A very last word on Branch Hazards 2/2

- X delayed slot: the X instructions after a branch are systematically executed

- The original SPARC and MIPS processors each used a single branch delay slot to eliminate single-cycle stalls after branches

- We need branch prediction... but nowadays, most of processors do it for us (and use slt...)!

- Some architectures have bypass between stages to avoid stalls

Avoid as possible floating points and jumps!

"Do you program in mips?" she asked. "nop", he said.

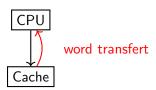

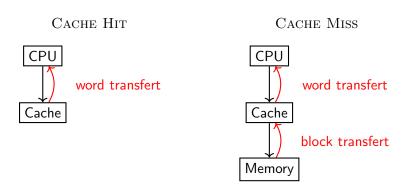

#### Stalls due to caches

When the processor processor needs to access a data:

- If data is in cache: with a cost of 3 cycles

- Otherwise: with a cost of 100 cycles

#### Stalls due to caches

When the processor processor needs to access a data:

- If data is in cache: with a cost of 3 cycles

- Otherwise: with a cost of 100 cycles

#### CACHE HIT

#### Stalls due to caches

When the processor processor needs to access a data:

- If data is in cache: with a cost of 3 cycles

- Otherwise: with a cost of 100 cycles

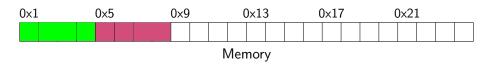

| 0×1 | 0×5 | 0×9 | 0×13 | 0×17 | 0×21 |

|-----|-----|-----|------|------|------|

|     |     |     |      |      |      |

Memory

| 0×1 | 0× | 5 |  | 0×9 |   | (   | )x13 | 3 | ( | )x1 | 7 | ( | )x2: | 1 |  |

|-----|----|---|--|-----|---|-----|------|---|---|-----|---|---|------|---|--|

|     |    |   |  |     |   |     |      |   |   |     |   |   |      |   |  |

|     |    |   |  |     | N | Лer | nor  | у |   |     |   |   |      |   |  |

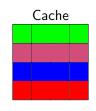

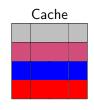

Access to adress 0x1, 4 words are fetched

Access to adress 0x5, 4 words are fetched

Access to adress 0x9, 4 words are fetched

Access to adress 0x13, 4 words are fetched

Access to adress 0x17, 4 words are fetched First line of cache is replaced!

Access to adress 0x21, 4 words are fetched Second line of cache is replaced!

#### Many strategies to put data into the cache:

- Direct Mapping:

- ► The address is decomposed in 3 parts: tag (8b), line (22b), and word(2b)

- Each block of main memory maps to only one cache line, i.e. block-size = cache-line-size

- Simple, Inexpensive, and fixed location for given block

- Associative Mapping:

- ► A main memory block can load into any line of cache

- Memory address is interpreted as tag and word

- Tag uniquely identifies block of memory

- Each block of main memory maps to only one cache line, i.e. block-size = cache-line-size

- Complex, Expensive, and no-fixed location for given block

### Prefetching

Fetch the data before it is needed (i.e. pre-fetch) by the program

- Eliminate cache misses

- Involves predicting which address will be needed in the future (as for branch prediction)

- In contrast to branch prediction:

- incorrect prefetched data will simply not be used

- there is no need for state recovery

#### Locality

- Locality is the principle that future memory accesses are near past accesses

- Memories take advantage of two types of locality

- ► Temporal locality, i.e. near in time: we will often access the same data again very soon

- ► Spatial locality, i.e. near in space/distance: our next access is often very close to our last access (or recent accesses)

#### Locality

- Locality is the principle that future memory accesses are near past accesses

- Memories take advantage of two types of locality

- ► Temporal locality, i.e. near in time: we will often access the same data again very soon

- Spatial locality, i.e. near in space/distance: our next access is often very close to our last access (or recent accesses)

Some Instruction Set Architecture (ISA) allows to pre-fetch some data: i.e., Humans or compilers has to insert (take advantage) of these instructions

#### Loops optimisations

We have already seen loops-unrolling to avoid stalls inside of the processor. Other techniques exist to avoid stalls due to cache:

- Loop Fission

- Loop interchanging

- Tabular Grouping

- Loop blocking

- Loop reversal

- Loop tiling

- . . .

Consider the following code, and direct mapping strategy:

```

int A[1024]; int B[1024]; int C[1024]; for (int i = 1; i<1024; ++i) {  A[i] = B[i]; \\ C[i] = C[i-1] + 1; \\ \}

```

Consider the following code, and direct mapping strategy:

```

int A[1024]; int B[1024]; int C[1024]; for (int i = 1; i<1024; ++i) {  A[i] = B[i]; \\ C[i] = C[i-1] + 1;  }

```

Fetch A[i], A[i + 1], A[i + 2] and A[i + 3]

Consider the following code, and direct mapping strategy:

```

int A[1024]; int B[1024]; int C[1024]; for (int i = 1; i<1024; ++i) {  A[i] = B[i]; \\ C[i] = C[i-1] + 1;  }

```

Fetch B[i], B[i + 1], B[i + 2] and B[i + 3]

Consider the following code, and direct mapping strategy:

```

int A[1024]; int B[1024]; int C[1024]; for (int i = 1; i<1024; ++i) {  A[i] = B[i]; \\ C[i] = C[i-1] + 1;  }

```

Fetch C[i], C[i+1], C[i+2] and C[i+3]

Consider the following code, and direct mapping strategy:

```

int A[1024]; int B[1024]; int C[1024]; for (int i = 1; i<1024; ++i) {  A[i] = B[i]; \\ C[i] = C[i-1] + 1; \\ \}

```

Fetch C[i-1] will probably conflict

- Hopefully A[i], B[i] and C[i] will not conflict in the cache

- but ... C[i-1] will probably!

#### Solution

Divide the loop into two:

- Less pressure on cache

- We can now insert padding to avoid conflicts

```

int A[1024]; padding[xx]; int B[1024]; int C[1024]; for (int i=1; i<1024; ++i) A[i] = B[i]; for (int i=1; i<1024; ++i) C[i] = C[i-1] + 1;

```

Try it by yourself in gcc -ftree-loop-distribution

## Loop interchanging 1/2

Consider the following code, and direct mapping cache:

```

int A[1024][1024];

for (int j = 1; j < 1024; ++j)

for (int i = 1; i < 1024; ++i)

A[j][i] = A[j][i] * 42;

```

In Fortran, the elements of an array are stored in memory contiguously by column, and the original loop iterates over rows, potentially creating at each access a cache miss

A B C

is stored A D B E C F

# Loop interchanging 1/2

Consider the following code, and direct mapping cache:

```

int A[1024][1024];

for (int i = 1; i < 1024; ++i)

for (int i = 1; i < 1024; ++i)

A[i][i] = A[i][i] * 42;

```

In Fortran, the elements of an array are stored in memory contiguously by column, and the original loop iterates over rows, potentially creating at

each access a cache miss

is stored

| A D B E C F |

|-------------|

|-------------|

# Loop interchanging 1/2

Consider the following code, and direct mapping cache:

```

int A[1024][1024];

for (int i = 1; i < 1024; ++i)

for (int i = 1; i < 1024; ++i)

A[i][i] = A[i][i] * 42;

```

Fetch A[

$$j + 1$$

][ $i$ ], A[ $j + 2$ ][ $i$ ], A[ $j + 3$ ][ $i$ ], and A[ $j + 4$ ][ $i$ ]

In Fortran, the elements of an array are stored in memory contiguously by column, and the original loop iterates over rows, potentially creating at

each access a cache miss

# Loop interchanging 2/2

#### Solution

This transformation switches the positions of one loop that is tightly nested within another loop.

```

int A[1024][1024];

for (int i = 1; i < 1024; ++i)

for (int j = 1; j < 1024; ++j)

A[j][i] = A[j][i] * 42;

```

Legal if the outermost loop does not carry any data dependence Try it by yourself in gcc -floop-interchange

Consider the following code, and direct mapping cache:

```

int A[1024]; int B[1024];

for (int j = 1; j < 1024; ++j)

A[j] = B[j] * 42;

```

Consider the following code, and direct mapping cache:

int A[1024]; int B[1024]; for (int

$$j = 1$$

;  $j < 1024$ ;  $++j$ )  $A[j] = B[j] * 42$ ;

Consider the following code, and direct mapping cache:

int A[1024]; int B[1024]; for (int

$$j = 1$$

;  $j < 1024$ ;  $++j$ )  $A[j] = B[j] * 42$ ;

Consider the following code, and direct mapping cache:

$$\begin{array}{l} \text{int A[1024]; int B[1024];} \\ \text{for (int } j=1; \ j{<}1024; \ +{+}j) \\ \text{A[}j] = \text{B[}j] * 42; \end{array}$$

Dynamic allocation does not allow padding. In the worst case, two miss per iterations

#### Solution

#### Group the two tabular into one

```

struct twoval {int A; int B};

struct twoval R[1024];

for (int j = 1; j < 1024; ++j)

R[j].A = R[j].B * 42;

```

Avoid a lot of caches miss!

Very hard for compiler to detect such cases

#### Loop Blocking

Consider the code below.

```

int A[1024][1024]; int B[1024][1024]; for (int i=1; i<1024; ++i) for (int j=1; j<1024; ++j) A[i][j] = B[i][j];

```

- If A and B are aligned we may encounter problems.

- Similar problems occur when processing images: A[i][j] = B[i-1][j-1] + B[i-1][j] + B[i-1][j+1] + B[i][j-1] + B[i][j] + B[i-1][j+1] + B[i+1][j] + B[i+1][j] + B[i+1][j+1];

- In this latter case, padding is complicated...

## Loop Blocking

#### Solution

Try to work with data that fit in memory!

```

int A[1024][1024]; int B[1024][1024]; for (int i = 1; i<1024; i += B) for (int j = 1; j<1024; j += B) for (int ii = 1; ii<min(1024, ii+B-1); ii += B) for (int jj = 1; jj< min(1024, ii+B-1); jj += B) A[i][j] = B[i][j];

```

#### Summary

- stalls in the processor can come from many reasons

- from data dependencies between instructions

- from instruction dependencies

- from cache and memory

- modern compiler hardly try to reduce them

- by using Instruction Level Parallelism (i.e, to have a lot of independent instructions)

- all these optimization must occur before register allocation (which is the final step)

- When writing a compiler, you must know the target processor by heart!

- Caches can be shared between many processors!